ELEE 2320 Chapter 2.

# Chapter 2

2.1. The proof is as follows:

$$(x + y) \cdot (x + z) = xx + xz + xy + yz$$

$$= x + xz + xy + yz$$

$$= x(1 + z + y) + yz$$

$$= x \cdot 1 + yz$$

$$= x + yz$$

2.2. The proof is as follows:

$$(x + y) \cdot (x + \overline{y}) = xx + xy + x\overline{y} + y\overline{y}$$

$$= x + xy + x\overline{y} + 0$$

$$= x(1 + y + \overline{y})$$

$$= x \cdot 1$$

$$= x$$

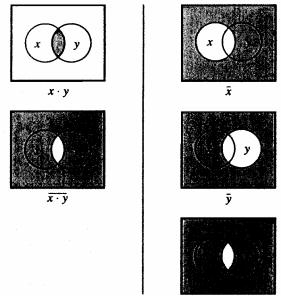

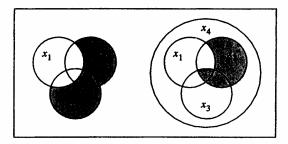

2.3. Proof using Venn diagrams:

$x + y \cdot z$

(x+y)(x+z)

2.4. Proof of 15a using Venn diagrams:

A similar proof is constructed for 15b.

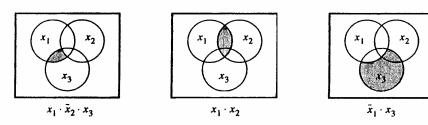

2.5. Proof using Venn diagrams:

- 2.6. A possible approach for determining whether or not the expressions are valid is to try to manipulate the left and right sides of an expression into the same form, using the theorems and properties presented in section 2.5. While this may seem simple, it is an awkward approach, because it is not obvious what target form one should try to reach. A much simpler approach is to construct a truth table for each side of an expression. If the truth tables are identical, then the expression is valid. Using this approach, we can show that the answers are:

- (a) Yes

- (b) Yes

- (c) No

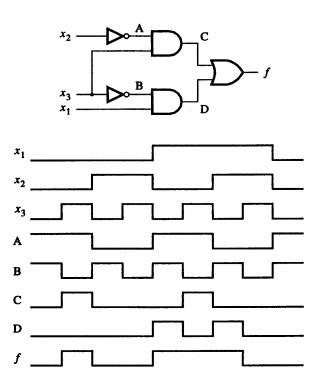

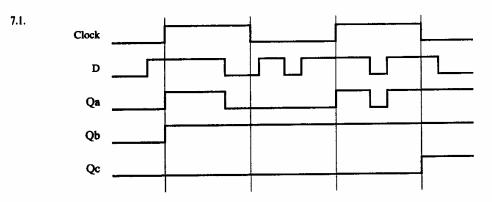

- 2.7. Timing diagram of the waveforms that can be observed on all wires of the circuit:

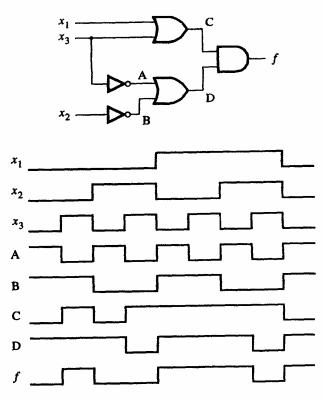

2.8. Timing diagram of the waveforms that can be observed on all wires of the circuit:

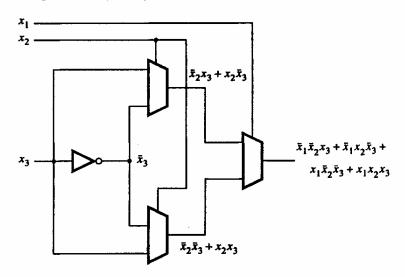

2.9. Starting with the canonical sum-of-products for f get

$$f = \overline{x}_1 \overline{x}_2 x_3 + \overline{x}_1 x_2 \overline{x}_3 + \overline{x}_1 x_2 x_3 + x_1 \overline{x}_2 \overline{x}_3 + x_1 \overline{x}_2 x_3 + x_1 x_2 \overline{x}_3 + x_1 \overline{x}_3 + x_1$$

2.10. The canonical product-of-sums for f is

$$f = (x_1 + x_2 + x_3)(x_1 + x_2 + \overline{x}_3)(x_1 + \overline{x}_2 + x_3)(x_1 + \overline{x}_2 + \overline{x}_3) \cdot (\overline{x}_1 + x_2 + x_3)(\overline{x}_1 + x_2 + \overline{x}_3)(\overline{x}_1 + \overline{x}_2 + x_3)$$

It can be manipulated as follows:

$$f = (x_1(1+x_2+x_3)(1+x_2+\overline{x}_3)(1+\overline{x}_2+x_3)(1+\overline{x}_2+\overline{x}_3)) \cdot (x_2(x_1+1+x_3)(x_1+1+\overline{x}_3)(\overline{x}_1+1+x_3)(\overline{x}_1+1+\overline{x}_3)) \cdot (x_3(x_1+x_2+1)(x_1+\overline{x}_2+1)(\overline{x}_1+x_2+1)(\overline{x}_1+\overline{x}_2+1))$$

...

$$= (x_1 \cdot 1 \cdot 1 \cdot 1 \cdot 1)(x_2 \cdot 1 \cdot 1 \cdot 1 \cdot 1)(x_3 \cdot 1 \cdot 1 \cdot 1 \cdot 1)$$

=  $x_1 x_2 x_3$

### 2.11. Derivation of the minimum sum-of-products expression:

$$f = x_1 x_3 + x_1 \overline{x}_2 + \overline{x}_1 x_2 x_3 + \overline{x}_1 \overline{x}_2 \overline{x}_3$$

=  $x_1 (\overline{x}_2 + x_2) x_3 + x_1 \overline{x}_2 (\overline{x}_3 + x_3) + \overline{x}_1 x_2 x_3 + \overline{x}_1 \overline{x}_2 \overline{x}_3$

=  $x_1 \overline{x}_2 x_3 + x_1 x_2 x_3 + x_1 \overline{x}_2 \overline{x}_3 + \overline{x}_1 x_2 x_3 + \overline{x}_1 \overline{x}_2 \overline{x}_3$

=  $x_1 x_3 + (x_1 + \overline{x}_1) x_2 x_3 + (x_1 + \overline{x}_1) \overline{x}_2 \overline{x}_3$

=  $x_1 x_3 + x_2 x_3 + \overline{x}_2 \overline{x}_3$

## 2.12. Derivation of the minimum sum-of-products expression:

$$f = x_1 \overline{x}_2 \overline{x}_3 + x_1 x_2 x_4 + x_1 \overline{x}_2 x_3 \overline{x}_4$$

=  $x_1 \overline{x}_2 \overline{x}_3 (\overline{x}_4 + x_4) + x_1 x_2 x_4 + x_1 \overline{x}_2 x_3 \overline{x}_4$

=  $x_1 \overline{x}_2 \overline{x}_3 \overline{x}_4 + x_1 \overline{x}_2 \overline{x}_3 x_4 + x_1 x_2 x_4 + x_1 \overline{x}_2 x_3 \overline{x}_4$

=  $x_1 \overline{x}_2 \overline{x}_3 + x_1 \overline{x}_2 (\overline{x}_3 + x_3) \overline{x}_4 + x_1 x_2 x_4$

=  $x_1 \overline{x}_2 \overline{x}_3 + x_1 \overline{x}_2 \overline{x}_4 + x_1 x_2 x_4$

#### 2.13. The simplest POS expression is derived as

$$f = (x_1 + x_3 + x_4)(x_1 + \overline{x}_2 + x_3)(x_1 + \overline{x}_2 + \overline{x}_3 + x_4)$$

$$= (x_1 + x_3 + x_4)(x_1 + \overline{x}_2 + x_3)(x_1 + \overline{x}_2 + x_3 + x_4)(x_1 + \overline{x}_2 + \overline{x}_3 + x_4)$$

$$= (x_1 + x_3 + x_4)(x_1 + \overline{x}_2 + x_3)((x_1 + \overline{x}_2 + x_4)(x_3 + \overline{x}_3))$$

$$= (x_1 + x_3 + x_4)(x_1 + \overline{x}_2 + x_3)(x_1 + \overline{x}_2 + x_4) \cdot 1$$

$$= (x_1 + x_3 + x_4)(x_1 + \overline{x}_2 + x_3)(x_1 + \overline{x}_2 + x_4)$$

#### 2.14. Derivation of the minimum product-of-sums expression:

$$f = (x_1 + x_2 + x_3)(x_1 + \overline{x}_2 + x_3)(\overline{x}_1 + \overline{x}_2 + x_3)(x_1 + x_2 + \overline{x}_3)$$

=  $((x_1 + x_2) + x_3)((x_1 + x_2) + \overline{x}_3)(x_1 + (\overline{x}_2 + x_3))(\overline{x}_1 + (\overline{x}_2 + x_3))$

=  $(x_1 + x_2)(\overline{x}_2 + x_3)$

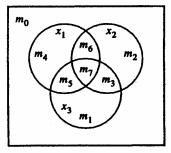

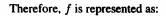

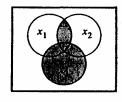

## 2.15. (a) Location of all minterms in a 3-variable Venn diagram:

(b) For  $f = x_1 \overline{x}_2 x_3 + x_1 x_2 + \overline{x}_1 x_3$  have:

$$f = x_3 + x_1 x_2$$

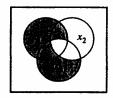

2.16. The function in Figure 2.18 in Venn diagram form is:

2.17. In Figure P2.1a it is possible to represent only 14 minterms. It is impossible to represent the minterms  $\overline{x}_1 \overline{x}_2 x_3 x_4$  and  $x_1 x_2 \overline{x}_3 \overline{x}_4$ .

In Figure P2.1b, it is impossible to represent the minterms  $x_1x_2\overline{x}_3\overline{x}_4$  and  $x_1x_2x_3\overline{x}_4$ .

2.18. Venn diagram for  $f = \overline{x}_1 \overline{x}_2 x_3 \overline{x}_4 + x_1 x_2 x_3 x_4 + \overline{x}_1 x_2$  is

2.19. The simplest SOP implementation of the function is

$$f = \overline{x}_1 x_2 x_3 + x_1 \overline{x}_2 \overline{x}_3 + x_1 x_2 \overline{x}_3 + x_1 x_2 x_3$$

=  $(\overline{x}_1 + x_1) x_2 x_3 + x_1 (\overline{x}_2 + x_2) \overline{x}_3$

=  $x_2 x_3 + x_1 \overline{x}_3$

#### 2.20. The simplest SOP implementation of the function is

$$f = \overline{x_1}\overline{x_2}x_3 + \overline{x_1}x_2x_3 + x_1\overline{x_2}\overline{x_3} + x_1x_2\overline{x_3} + x_1x_2x_3$$

=  $\overline{x_1}(\overline{x_2} + x_2)x_3 + x_1(\overline{x_2} + x_2)\overline{x_3} + (\overline{x_1} + x_1)x_2x_3$

=  $\overline{x_1}x_3 + x_1\overline{x_3} + x_2x_3$

Another possibility is

$$f = \overline{x}_1 x_3 + x_1 \overline{x}_3 + x_1 x_2$$

2.21. The simplest POS implementation of the function is

$$f = (x_1 + x_2 + x_3)(x_1 + \overline{x}_2 + x_3)(\overline{x}_1 + x_2 + \overline{x}_3)$$

=  $((x_1 + x_3) + x_2)((x_1 + x_3) + \overline{x}_2)(\overline{x}_1 + x_2 + \overline{x}_3)$

=  $(x_1 + x_3)(\overline{x}_1 + x_2 + \overline{x}_3)$

### 2.22. The simplest POS implementation of the function is

$$f = (x_1 + x_2 + x_3)(x_1 + x_2 + \overline{x}_3)(\overline{x}_1 + x_2 + \overline{x}_3)(\overline{x}_1 + \overline{x}_2 + \overline{x}_3)$$

=  $((x_1 + x_2) + x_3)((x_1 + x_2) + \overline{x}_3)((\overline{x}_1 + x_3) + x_2)((\overline{x}_1 + x_3) + \overline{x}_2)$

=  $(x_1 + x_2)(\overline{x}_1 + \overline{x}_3)$

2.23. The lowest cost circuit is defined by

$$f(x_1, x_2, x_3) = x_1x_2 + x_1x_3 + x_2x_3$$

2.24. The truth table that corresponds to the timing diagram in Figure P2.3 is

|     | <b>x</b> 1 | $x_2$ | <b>x</b> 3 | f |

|-----|------------|-------|------------|---|

|     | 0          | 0     | 0          | 1 |

|     | 0          | 0     | 1          | 0 |

| 1   | 0          | 1     | 0          | 0 |

| ; ( | 0          | 1     | 1          | 1 |

|     | 1          | 0     | 0          | 0 |

|     | 1          | . 0 . | 1          | 1 |

|     | 1          | 1     | 0          | 1 |

|     | 1          | 1     | 1          | 0 |

The simplest SOP expression is  $f = \overline{x}_1 \overline{x}_2 \overline{x}_3 + \overline{x}_1 x_2 x_3 + x_1 \overline{x}_2 x_3 + x_1 x_2 \overline{x}_3$ .

2.25. The truth table that corresponds to the timing diagram in Figure P2.4 is

| $\boldsymbol{x_1}$ | $x_2$ | <b>x</b> 3 | f |

|--------------------|-------|------------|---|

| 0                  | 0     | 0          | 0 |

| 0                  | 0     | 1          | 1 |

| 0                  | 1     | 0          | 1 |

| 0                  | 1     | 1          | 1 |

| 1                  | 0     | 0          | 1 |

| 1                  | 0     | 1          | 0 |

| 1                  | 1     | 0          | 0 |

| 1                  | 1     | 1          | 1 |

The simplest SOP expression is derived as follows:

$$f = \overline{x_1} \overline{x_2} x_3 + \overline{x_1} x_2 \overline{x_3} + \overline{x_1} x_2 x_3 + x_1 \overline{x_2} \overline{x_3} + x_1 x_2 x_3$$

$$= \overline{x_1} (\overline{x_2} + x_2) x_3 + \overline{x_1} \overline{x_2} (\overline{x_3} + x_3) + (\overline{x_1} + x_1) x_2 x_3 + x_1 \overline{x_2} \overline{x_3}$$

$$= \overline{x_1} \cdot 1 \cdot x_3 + \overline{x_1} x_2 \cdot 1 + 1 \cdot x_2 x_3 + x_1 \overline{x_2} \overline{x_3}$$

$$= \overline{x_1} x_3 + \overline{x_1} x_2 + x_2 x_3 + x_1 \overline{x_2} \overline{x_3}$$

2.26. (a)

| <i>x</i> <sub>1</sub> | $x_0$ | $y_1$ | <b>y</b> o | f |

|-----------------------|-------|-------|------------|---|

| 0                     | 0     | 0     | 0          | 1 |

| 0                     | 0     | 0     | 1          | 0 |

| 0                     | 0     | 1     | 0          | 0 |

| 0                     | 0     | 1     | 1          | 0 |

| 0                     | 1     | 0     | 0          | 0 |

| 0                     | 1     | 0     | 1          | 1 |

| 0                     | 1     | 1     | 0          | 0 |

| 0                     | 1     | 1     | 1          | 0 |

| 1                     | 0     | 0     | 0          | 0 |

| 1                     | 0     | 0     | 1          | 0 |

| 1                     | 0     | 1     | 0          | 1 |

| 1                     | 0     | 1     | 1          | 0 |

| 1                     | 1     | 0     | 0          | 0 |

| 1                     | 1     | 0     | 1          | 0 |

| 1                     | 1     | 1     | 0          | 0 |

| 1                     | 1     | 1     | 1          | 1 |

(b)

$$f = (x_1 + \overline{y}_1)(\overline{x}_1 + y_1)(x_0 + \overline{y}_0)(\overline{x}_0 + y_0)$$

2.27. (a)

| <i>x</i> <sub>1</sub> | $x_0$ | <b>y</b> 1 | <b>y</b> o | f |

|-----------------------|-------|------------|------------|---|

| 0                     | 0     | 0          | 0          | 1 |

| 0                     | 0     | 0          | 1          | 0 |

| 0                     | 0     | 1          | 0          | 0 |

| 0                     | 0     | 1          | 1          | 0 |

| 0                     | 1     | 0          | 0          | 1 |

| 0                     | 1     | 0          | 1          | 1 |

| 0                     | 1     | 1          | 0          | 0 |

| 0                     | 1     | 1          | 1          | 0 |

| 1                     | 0     | 0          | 0          | 1 |

| 1                     | 0     | 0          | 1          | 1 |

| 1                     | 0     | 1          | 0          | 1 |

| 1                     | 0     | 1          | 1          | 0 |

| 1                     | 1     | 0          | 0          | 1 |

| 1                     | 1     | 0          | 1          | 1 |

| 1                     | 1     | 1          | 0          | 1 |

| 1                     | 1     | 1          | 1          | 1 |

(b) The canonical SOP expression is

$$f = \overline{x_1}\overline{x_0}\overline{y_1}\overline{y_0} + \overline{x_1}x_0\overline{y_1}\overline{y_0} + \overline{x_1}x_0\overline{y_1}y_0 + x_1\overline{x_0}\overline{y_1}\overline{y_0} + x_1\overline{x_0}\overline{y_1}y_0 + x_1\overline{x_0}y_1\overline{y_0} + x_1\overline{x_0}y_1\overline{y_0} + x_1x_0\overline{y_1}\overline{y_0} + x_1x_0\overline{y_1}$$

(c) The simplest SOP expression is

$f = x_1 x_0 + \overline{y}_1 \overline{y}_0 + x_1 \overline{y}_0 + x_0 \overline{y}_1$

2.30.

LIBRARY iece; USE iece.std\_logic\_1164.all;

ENTITY prob2\_30 IS PORT ( x1, x2, x3, x4 : IN STD\_LOGIC ; f1, f2 : OUT STD\_LOGIC ) ; END prob2\_30 ;

ARCHITECTURE LogicFunc OF prob2\_30 IS BEGIN f1 <= (x1 AND NOT x3) OR (x2 AND NOT x3) OR NOT x3 AND NOT x4) OR (x1 AND x2) OR x1 AND NOT x4); f2 <= (x1 OR NOT x3) AND (x1 OR x2 OR NOT x4) AND x2 OR NOT x3 OR NOT x4);

- END LogicFunc ;

- 2.31. For the functions given in this question, it is not true that  $f_1 = \overline{f}_2$ . The function  $f_1$  is given in the form (SOP-term) AND (SOP-term). If these same two SOP terms are used for the *different* function  $f_1 = ($ SOP-term) OR (SOP-term) then for this new  $f_1$  it is true that  $f_1 = \overline{f}_2$ . Complete VHDL code using this new function  $f_1$  is shown below.

LIBRARY ieee : USE ieee.std\_logic\_1164.all; ENTITY prob2\_31 IS PORT  $(x1, x2, x3, x4 : IN STD_LOGIC;$ : OUT STD\_LOGIC); f1, f2 END prob2\_31; ARCHITECTURE LogicFunc OF prob2\_31 IS BEGIN  $f1 \leq ((x1 AND x3) OR (NOT x1 AND NOT x3)) OR$ ((x2 AND x4) OR (NOT x2 AND NOT x4)); f2 <= (x1 AND x2 AND NOT x3 AND NOT x4) OR (NOT x1 AND NOT x2 AND x3 AND x4) OR (x1 AND NOT x2 AND NOT x3 AND x4) OR (NOT x1 AND x2 AND x3 AND NOT x4); END LogicFunc ;

Thank you Abe Aounallah.

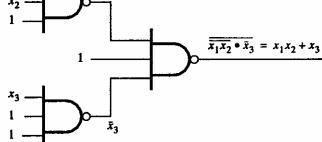

## **Chapter 3**

| 3.1. (a) |                | $x_1 x_2 x_3$                 | f                                    |     |

|----------|----------------|-------------------------------|--------------------------------------|-----|

|          |                | 0 0 0                         | 0                                    |     |

|          |                | 0 0 1                         | 1                                    |     |

|          |                | 0 1 0                         | 1                                    |     |

|          |                | 0 1 1                         | 0                                    |     |

|          |                | 1 0 0                         | 1                                    |     |

|          |                | 1 0 1                         | 0                                    |     |

|          |                | 1 1 0                         | 0                                    |     |

|          |                | 1 1 1                         | 1                                    |     |

|          |                |                               |                                      |     |

| (b)      | #transistors = | = NOT_gates ×                 | $2 + AND_{gates} \times 8 + OR_{ga}$ | tes |

|          | =              | $= 3 \times 2 + 4 \times 8 -$ | $+1 \times 10 = 48$                  |     |

3.2. (a) In problem 3.1 the canonical SOP for f is

$f = \overline{x}_1 \overline{x}_2 x_3 + \overline{x}_1 x_2 \overline{x}_3 + x_1 \overline{x}_2 \overline{x}_3 + x_1 x_2 x_3$

This expression is equivalent to f in Figure P3.2, as derived below.

(b) Assuming the multiplexers are implemented using transmission gates

#transistors = NOT\_gates  $\times 2 + MUXes \times 6$ =  $1 \times 2 + 3 \times 6 = 20$  3.3. (a) A SOP expression for f in Figure P3.3 is:

$$f = (x_1 \oplus x_2) \oplus x_3$$

=  $(x_1 \oplus x_2)\overline{x}_3 + \overline{(x_1 \oplus x_2)}x_3$

=  $x_1\overline{x}_2\overline{x}_3 + \overline{x}_1x_2\overline{x}_3 + \overline{x}_1\overline{x}_2x_3 + x_1x_2x_3$

which is equivalent to the expression derived in problem 3.2.

(b) Assuming the XOR gates are implemented as shown in Figure 3.61b

$$\# \text{transistors} = \text{XOR}_{\text{gates}} \times 8$$

$$= 2 \times 8 = 16$$

3.4. Using the circuit

The number of transistors needed is 16.

3.5. Using the circuit

The number of transistors needed is 20.

3.6. (a)

| <i>x</i> 1 | <i>x</i> <sub>2</sub> | x3 | <u> </u> |

|------------|-----------------------|----|----------|

| 0          | 0                     | 0  | 1        |

| 0          | 0                     | 1  | 1        |

| 0          | 1                     | 0  | 1        |

| 0          | 1                     | 1  | 1        |

| 1          | 0                     | 0  | 1        |

| 1          | 0                     | 1  | 0        |

| 1          | 1                     | 0  | 0        |

| 1          | 1                     | 1  | 0        |

|            |                       |    |          |

(b) The canonical SOP expression is

$$f = \overline{x}_1 \overline{x}_2 \overline{x}_3 + \overline{x}_1 \overline{x}_2 x_3 + \overline{x}_1 x_2 \overline{x}_3 + \overline{x}_1 x_2 x_3 + x_1 \overline{x}_2 \overline{x}_3$$

The number of transistors required using only AND, OR, and NOT gates is

#transistors = NOT\_gates  $\times 2$  + AND\_gates  $\times 8$  + OR\_gates  $\times 12$ =  $3 \times 2 + 5 \times 8 + 1 \times 12 = 58$

3.7. (a)

| <i>x</i> 1 | <i>x</i> 2 | <i>x</i> 3 | <i>x</i> 4 | f | _ | x <sub>i</sub> | <i>x</i> <sub>2</sub> | <i>x</i> <sub>3</sub> | x <sub>4</sub> | f |

|------------|------------|------------|------------|---|---|----------------|-----------------------|-----------------------|----------------|---|

| 0          | 0          | 0          | 0          | 1 |   | 1              | 0                     | 0                     | 0              | 1 |

| 0          | 0          | 0          | 1          | 0 |   | 1              | 0                     | 0                     | 1              | 0 |

| 0          | 0          | 1          | 0          | 0 |   | 1              | 0                     | 1                     | 0              | 0 |

| 0          | 0          | 1          | 1          | 0 |   | 1              | 0                     | 1                     | 1              | 0 |

| 0          | 1          | 0          | 0          | 1 |   | 1              | 1                     | 0                     | 0              | 0 |

| 0          | 1          | 0          | 1          | 0 |   | 1              | 1                     | 0                     | 1              | 0 |

| 0          | 1          | 1          | 0          | 0 |   | 1              | 1                     | 1                     | 0              | 0 |

| 0          | 1          | 1          | 1          | 0 |   | 1              | 1                     | 1                     | 1              | 0 |

**(b)**

$f = \overline{x}_1 \overline{x}_2 \overline{x}_3 \overline{x}_4 + \overline{x}_1 x_2 \overline{x}_3 \overline{x}_4 + x_1 \overline{x}_2 \overline{x}_3 \overline{x}_4$  $= \overline{x}_1 \overline{x}_3 \overline{x}_4 + \overline{x}_2 \overline{x}_3 \overline{x}_4$

The number of transistors required using only AND, OR, and NOT gates is

#transistors = NOT\_gates

$$\times 2$$

+ AND\_gates  $\times 8$  + OR\_gates  $\times 4$

=  $4 \times 2 + 2 \times 8 + 1 \times 4 = 28$

3.8.

3.10. Minimum SOP expression for f is

$$f = \overline{x}_2 \overline{x}_3 + \overline{x}_1 \overline{x}_3 + \overline{x}_2 \overline{x}_4 + \overline{x}_1 \overline{x}_4$$

$$= (\overline{x}_1 + \overline{x}_2)(\overline{x}_3 + \overline{x}_4)$$

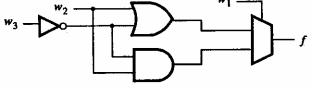

which leads to the circuit

3.11. Minimum SOP expression for f is

$$f = \overline{x}_4 + \overline{x}_1 \overline{x}_2 \overline{x}_3$$

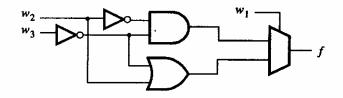

which leads to the circuit

3.9.

3.12.

3.14. (a) Since  $V_{DS} \ge V_{GS} - V_T$  the NMOS transistor is operating in the saturation region:

$$I_D = \frac{1}{2} k'_n \frac{W}{L} (V_{GS} - V_T)^2$$

= 10  $\frac{\mu A}{V^2} \times 5 \times (5 V - 1 V)^2 = 800 \,\mu A$

(b) In this case  $V_{DS} < V_{GS} - V_T$ , thus the NMOS transistor is operating in the triode region:

$$\begin{split} I_D &= k'_n \frac{W}{L} \left[ (V_{GS} - V_T) V_{DS} - \frac{1}{2} V_{DS}^2 \right] \\ &= 20 \frac{\mu A}{V^2} \times 5 \times \left[ (5 V - 1 V) \times 0.2 V - \frac{1}{2} \times (0.2 V)^2 \right] = 78 \,\mu A \end{split}$$

3.15. (a) Since  $V_{DS} \leq V_{GS} - V_T$  the PMOS transistor is operating in the saturation region:

$$I_D = \frac{1}{2} k'_p \frac{W}{L} (V_{GS} - V_T)^2$$

=  $5 \frac{\mu A}{V^2} \times 5 \times (-5 V + 1 V)^2 = 400 \,\mu A$

(b) In this case  $V_{DS} > V_{GS} - V_T$ , thus the PMOS transistor is operating in the triode region:

$$I_D = k'_p \frac{W}{L} \left[ (V_{GS} - V_T) V_{DS} - \frac{1}{2} V_{DS}^2 \right]$$

=  $10 \frac{\mu A}{V^2} \times 5 \times \left[ (-5 V + 1 V) \times (-0.2) V - \frac{1}{2} \times (-0.2 V)^2 \right] = 39 \,\mu A$

3.16.

$$R_{DS} = 1 / \left[ k'_n \frac{W}{L} (V_{GS} - V_T) \right]$$

= 1 /  $\left[ 0.020 \frac{\text{mA}}{\text{V}^2} \times 10 \times (5 \text{ V} - 1 \text{ V}) \right] = 1.25 \text{ k}\Omega$

3.17.

$$R_{DS} = 1 / \left[ k'_n \frac{W}{L} (V_{GS} - V_T) \right]$$

= 1 /  $\left[ 0.040 \frac{\text{mA}}{\text{V}^2} \times 10 \times (3.3 \text{ V} - 0.66 \text{ V}) \right] = 947 \Omega$

3.18. Since  $V_{DS} < (V_{GS} - V_T)$ , the PMOS transistor is operating in the saturation region:

$$I_{SD} = \frac{1}{2} k'_p \frac{W}{L} (V_{GS} - V_T)^2$$

=  $50 \frac{\mu A}{V^2} \times (-5 V + 1 V)^2 = 800 \,\mu A$

Hence the value of  $R_{DS}$  is

$$R_{DS} = V_{DS}/I_{DS}$$

= 4.8 V/800 \mu A = 6 k\Omega

3.19. Since  $V_{DS} < (V_{GS} - V_T)$ , the PMOS transistor is operating in the saturation region:

$$I_{SD} = \frac{1}{2} k'_p \frac{W}{L} (V_{GS} - V_T)^2$$

= 80  $\frac{\mu A}{V^2} \times (-3.3 V + 0.66 V)^2 = 558 \,\mu A$

Hence the value of  $R_{DS}$  is

$$R_{DS} = V_{DS}/I_{DS}$$

= 3.2 V/558  $\mu$ A = 5.7 k $\Omega$

3.20. The low output voltage of the pseudo-NMOS inverter can be obtained by setting  $V_x = V_{DD}$  and evaluating the voltage  $V_f$ . First we assume that the NMOS transistor is operating in the triode region while the PMOS is operating in the saturation region. For simplicity we will assume that the magnitude of the threshold voltages for both the NMOS and PMOS transistors are equal, so that

$$V_T = V_{TN} = -V_{TP}$$

The current flowing through the PMOS transistor is

$$I_D = \frac{1}{2} k'_p \frac{W_p}{L_p} (-V_{DD} - V_{TP})^2$$

=  $\frac{1}{2} k_p (-V_{DD} - V_{TP})^2$

=  $\frac{1}{2} k_p (V_{DD} - V_T)^2$

Similarly, the current going through the NMOS transistor is

$$I_D = k'_n \frac{W_n}{L_n} \left[ (V_x - V_{TN}) V_f - \frac{1}{2} V_f^2 \right]$$

=  $k_n \left[ (V_x - V_{TN}) V_f - \frac{1}{2} V_f^2 \right]$

=  $k_n \left[ (V_{DD} - V_T) V_f - \frac{1}{2} V_f^2 \right]$

Since there is only one path for current to flow, we can equate the currents flowing through the NMOS and PMOS transistors and solve for the voltage  $V_f$ .

$$k_p (V_{DD} - V_T)^2 = 2k_n \left[ (V_{DD} - V_T) V_f - \frac{1}{2} V_f^2 \right]$$

$$k_p (V_{DD} - V_T)^2 - 2k_n (V_{DD} - V_T) V_f + k_n V_f^2 = 0$$

This quadratic equation can be solved using the standard formula, with the parameters

$$a = k_n, \ b = -2k_n(V_{DD} - V_T), \ c = k_p(V_{DD} - V_T)^2$$

which gives

$$V_{f} = \frac{-b}{2a} \pm \sqrt{\frac{b^{2}}{4a^{2}} - \frac{c}{a}}$$

=  $(V_{DD} - V_{T}) \pm \sqrt{(V_{DD} - V_{T})^{2} - \frac{k_{p}}{k_{n}}(V_{DD} - V_{T})^{2}}$

=  $(V_{DD} - V_{T}) \left[ 1 \pm \sqrt{1 - \frac{k_{p}}{k_{n}}} \right]$

Only one of these two solutions is valid, because we started with the assumption that the NMOS transistor is in the triode region while the PMOS is in the saturation region. Thus

$$V_f = (V_{DD} - V_T) \left[ 1 - \sqrt{1 - \frac{k_p}{k_n}} \right]$$

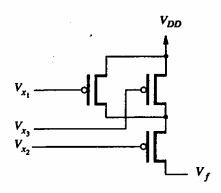

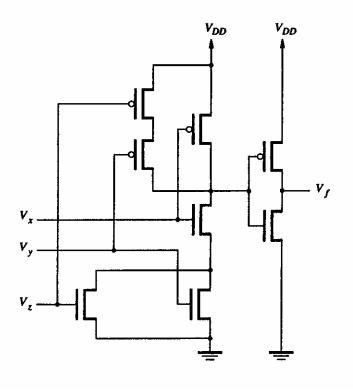

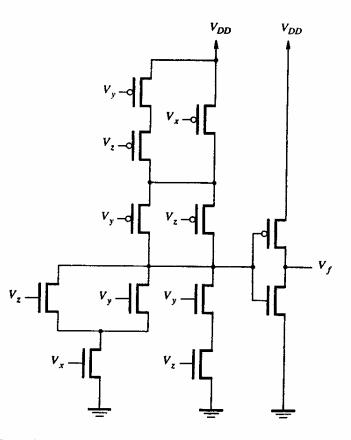

3.21. (a)

$$I_{stat} = \frac{1}{2} k'_p \frac{W_p}{L_p} (V_{DD} - V_T)^2$$

=  $12 \frac{\mu A}{V^2} \times 1 \times (5 V - 1 V)^2 = 192 \mu A$

**(b)**

$$R_{DS} = 1 / \left[ k'_n \frac{W_n}{L_n} (V_{GS} - V_T) \right]$$

= 1 /  $\left[ 0.060 \frac{\text{mA}}{\text{V}^2} \times 4 \times (5 \text{ V} - 1 \text{ V}) \right] = 1.04 \text{ k}\Omega$

$$k_p = k'_p \frac{W_p}{L_p} = 24 \frac{\mu A}{V^2}$$

$$k_n = k'_n \frac{W_n}{L_n} = 240 \frac{\mu A}{V^2}$$

$$V_{OL} = V_f = (5 \text{ V} - 1 \text{ V}) \left[ 1 - \sqrt{1 - \frac{24}{240}} \right]$$

= 0.21 V

$$P_D = I_{stat}V_{DD}$$

= 192 \mm A \times 5 V = 960 \mm W \approx 1mW

(e)

$$R_{SDP} = V_{SD}/I_{SD}$$

=  $(V_{DD} - V_f)/I_{stat}$

=  $(5 V - 0.21 V)/0.192 mA = 24.9 k\Omega$

(f) The low-to-high propagation delay is

$$t_{p_{LH}} = \frac{1.7C}{k'_p \frac{W_p}{L_p} V_{DD}} \\ = \frac{1.7 \times 70 \text{ fF}}{24 \frac{\mu A}{V^2} \times 1 \times 5 \text{ V}} = 0.99 \text{ ns}$$

The high-to-low propagation delay is

$$t_{p_{HL}} = \frac{1.7C}{k'_n \frac{W_n}{L_n} V_{DD}} \\ = \frac{1.7 \times 70 \text{ fF}}{60 \frac{\mu A}{V^2} \times 4 \times 5 \text{ V}} = 0.1 \text{ ns}$$

3.22. (a)

$$I_{stat} = \frac{1}{2} k'_p \frac{W_p}{L_p} (V_{DD} - V_T)^2$$

=  $48 \frac{\mu A}{V^2} \times 1 \times (5 V - 1 V)^2 = 768 \,\mu A$

(b)

$$R_{DS} = 1 / \left[ k'_n \frac{W_n}{L_n} (V_{GS} - V_T) \right]$$

= 1 /  $\left[ 0.060 \frac{\text{mA}}{\text{V}^2} \times 4 \times (5 \text{ V} - 1 \text{ V}) \right] = 1.04 \text{ k}\Omega$

$$k_p = k'_p \frac{W_p}{L_p} = 96 \frac{\mu A}{V^2} k_n = k'_n \frac{W_n}{L_n} = 240 \frac{\mu A}{V^2}$$

$$V_{OL} = V_f = (5 \text{ V} - 1 \text{ V}) \left[ 1 - \sqrt{1 - \frac{96}{240}} \right]$$

= 0.90 V

$$P_D = I_{stat}V_{DD}$$

= 768 \mu A \times 5 V = 3840 \mu W \approx 3.8mW

(e)

$$R_{SDP} = V_{SD}/I_{SD}$$

=  $(V_{DD} - V_f)/I_{stat}$

=  $(5 V - 0.90 V)/0.768 mA = 5.34 k\Omega$

(f) The low-to-high propagation delay is

$$t_{p_{LH}} = \frac{1.7C}{k'_{p} \frac{W_{p}}{L_{p}} V_{DD}}$$

=  $\frac{1.7 \times 70 \text{ fF}}{96 \frac{\mu A}{V2} \times 1 \times 5 \text{ V}} = 0.25 \text{ ns}$

The high-to-low propagation delay is

$$t_{PHL} = \frac{1.7C}{k'_n \frac{W_n}{L_n} V_{DD}} \\ = \frac{1.7 \times 70 \text{ fF}}{60 \frac{\mu A}{V^2} \times 4 \times 5 \text{ V}} = 0.1 \text{ ns}$$

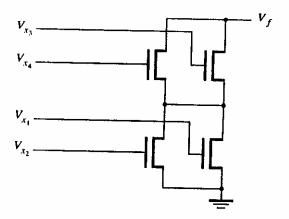

3.23. (a)

$$I_{stat} = \frac{1}{2} k'_p \frac{W_p}{L_p} (V_{DD} - V_T)^2$$

=  $12 \frac{\mu A}{V^2} \times 1 \times (5 V - 1 V)^2 = 192 \mu A$

(b) The two NMOS transistors in series can be considered equivalent to a single transistor with twice the length. Thus

$$R_{DS} = 1 / \left[ k'_n \frac{W_n}{L_n} (V_{GS} - V_T) \right]$$

= 1 /  $\left[ 0.060 \frac{\text{mA}}{\text{V}^2} \times 2 \times (5 \text{ V} - 1 \text{ V}) \right] = 2.08 \text{ k}\Omega$

$$k_p = k'_p \frac{W_p}{L_p} = 24 \frac{\mu A}{V^2}$$

$$k_n = k'_n \frac{W_n}{L_n} = 120 \frac{\mu A}{V^2}$$

$$V_{OL} = V_f = (5 \text{ V} - 1 \cdot \text{V}) \left[ 1 - \sqrt{1 - \frac{24}{120}} \right]$$

= 0.42 V

$$P_D = I_{stat} V_{DD}$$

= 192 \mu A \times 5 V = 960 \mu W \approx 1mW

(e)

$$R_{SDP} = V_{SD}/I_{SD}$$

=  $(V_{DD} - V_f)/I_{stat}$

=  $(5 V - 0.42 V)/0.192 mA = 23.9 k\Omega$

(f) The low-to-high propagation delay is

$$t_{p_{LH}} = \frac{1.7C}{k'_{p} \frac{W_{p}}{L_{p}} V_{DD}}$$

=  $\frac{1.7 \times 70 \text{ fF}}{24 \frac{\mu A}{T} \times 1 \times 5 \text{ V}} = 0.99 \text{ ns}$

The high-to-low propagation delay is

$$t_{PHL} = \frac{1.7C}{k'_n \frac{W_n}{L_n} V_{DD}} \\ = \frac{1.7 \times 70 \text{ fF}}{60 \frac{\mu A}{2} \times 2 \times 5 \text{ V}} = 0.2 \text{ ns}$$

3.24. (a)

$$I_{stat} = \frac{1}{2} k'_p \frac{W_p}{L_p} (V_{DD} - V_T)^2$$

=  $12 \frac{\mu A}{V^2} \times 1 \times (5 V - 1 V)^2 = 192 \mu A$

(b) The two NMOS transistors in parallel can be considered equivalent to a single transistor with twice the width. Thus

$$R_{DS} = 1 / \left[ k'_n \frac{W_n}{L_n} (V_{GS} - V_T) \right]$$

= 1 /  $\left[ 0.060 \frac{\text{mA}}{\text{V}^2} \times 8 \times (5 \text{ V} - 1 \text{ V}) \right] = 520 \Omega$

$$k_p = k'_p \frac{W_p}{L_p} = 24 \frac{\mu A}{V^2}$$

$$k_n = k'_n \frac{W_n}{L_n} = 480 \frac{\mu A}{V^2}$$

$$V_{OL} = V_f = (5 \text{ V} - 1 \text{ V}) \left[ 1 - \sqrt{1 - \frac{24}{480}} \right]$$

= 0.10 V

$$P_D = I_{stat} V_{DD}$$

= 192 \mu A \times 5 V = 960 \mu W \approx 1mW

(e)

$$R_{SDP} = V_{SD}/I_{SD}$$

=  $(V_{DD} - V_f)/I_{stat}$

=  $(5 V - 0.10 V)/0.192 mA = 25.5 k\Omega$

(f) The low-to-high propagation delay is

$$t_{p_{LH}} = \frac{1.7C}{k'_p \frac{W_p}{L_p} V_{DD}}$$

$$= \frac{1.7 \times 70 \text{ fF}}{24 \frac{\mu A}{V^2} \times 1 \times 5 \text{ V}} = 0.99 \text{ ns}$$

The high-to-low propagation delay is

$$t_{p_{HL}} = \frac{1.7C}{k'_n \frac{W_n}{L_n} V_{DD}} \\ = \frac{1.7 \times 70 \text{ fF}}{60 \frac{\mu A}{2} \times 8 \times 5 \text{ V}} = 0.05 \text{ ns}$$

3.25. (a)

$$NM_H = V_{OH} - V_{IH} = 0.5 V$$

$$NM_L = V_{IL} - V_{OL} = 0.7 V$$

**(b)**

$$V_{OL} = 8 \times 0.1 \text{ V} = 0.8 \text{ V}$$

$NM_L = 1 \text{ V} - 0.8 \text{ V} = 0.2 \text{ V}$

3.26. Under steady-state conditions, for an n-input CMOS NAND gate the voltage levels  $V_{OL}$  and  $V_{OH}$  are 0 V and  $V_{DD}$ , respectively. No current flows in a CMOS gate in the steady-state. Thus there can be no voltage drop across any of the transistors.

3.27. (a)

(b)

$$P_{NOT\_gate} = fCV^2$$

$= 75 \text{ MHz} \times 150 \text{ fF} \times (5 \text{ V})^2 = 281 \,\mu\text{W}$

$P_{total} = 0.2 \times 250,000 \times 281 \,\mu\text{W} = 14 \,\text{W}$

3.28. (a)

$$P_{NOT\_gate} = fCV^2$$

= 125 MHz × 120 fF × (3.3 V)<sup>2</sup> = 163  $\mu$ W

(b)

$$P_{total} = 0.2 \times 250,000 \times 163 \,\mu\text{W} = 8.2 \,\text{W}$$

3.29. (a) The high-to-low propagation delay is

$$t_{p_{HL}} = \frac{1.7C}{k'_n \frac{W_n}{L_n} V_{DD}} = \frac{1.7 \times 150 \text{ fF}}{20 \frac{\#\Lambda}{V^2} \times 10 \times 5 \text{ V}} = 0.255 \text{ ns}$$

(b) The low-to-high propagation delay is

$$t_{PLH} = \frac{1.7C}{k_p^{\prime} \frac{W_{\mu}}{L_{\mu}} V_{DD}} = \frac{1.7 \times 150 \, \text{fF}}{8 \, \frac{\mu \text{A}}{\text{V}^2} \times 10 \times 5 \, \text{V}} = 0.638 \, \text{ns}$$

(c) For equivalent high-to-low and low-to-high delays

$$t_{pHL} = t_{pLH}$$

$$\frac{1.7C}{k'_n \frac{W_n}{L_n} V_D D} = \frac{1.7C}{k'_p \frac{W_p}{L_p} V_D D}$$

$$\frac{W_p}{L_p} = \frac{\frac{k'_n}{k'_p} W_n}{L_n}$$

$$= \frac{12.5 \,\mu\text{m}}{0.5 \,\mu\text{m}}$$

3.30. (a) The high-to-low propagation delay is

$$t_{PHL} = \frac{1.7C}{k'_n \frac{W_n}{L_n} V_{DD}} = \frac{1.7 \times 150 \text{ fF}}{40 \frac{\mu A}{V^2} \times 10 \times 3.3 \text{ V}} = 0.193 \text{ ns}$$

(b) The low-to-high propagation delay is

$$t_{p_{LH}} = \frac{1.7C}{k'_p \frac{W_p}{L_s} V_{DD}} = \frac{1.7 \times 150 \,\mathrm{fF}}{16 \,\frac{\mu A}{V^2} \times 10 \times 3.3 \,\mathrm{V}} = 0.483 \,\mathrm{ns}$$

(c) For equivalent high-to-low and low-to-high delays

$$\frac{t_{p_{HL}}}{\frac{1.7C}{k'_n \frac{W_n}{L_n} V_D D}} = \frac{t_{p_{LH}}}{\frac{1.7C}{k'_p \frac{W_p}{L_p} V_D D}}$$

$$\frac{W_p}{L_p} = \frac{\frac{k'_n}{k_p} W_n}{L_n}$$

$$= \frac{8.75 \,\mu\text{m}}{0.35 \,\mu\text{m}}$$

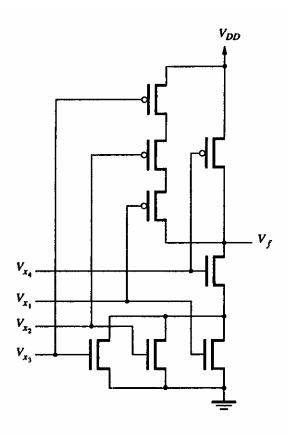

3.31. The two PMOS transistors in a CMOS NAND gate are connected in parallel. The worst case current to drive the output high happens when only one of these transistors is turned "ON". Thus each transistor has to have the same dimensions as the PMOS transistor in the inverter, namely  $\frac{W_p}{L_p} = 4$ .

The two NMOS transistors are connected in series. If each one had the ratio  $\frac{W_n}{L_n}$ , then the two transistors could be thought of as one equivalent transistor with a  $\frac{W_n}{2L_n}$  ratio. Thus each NMOS transistor must have twice the width of that in the inverter, namely  $\frac{W_n}{L_n} = 4$ .

3.32. The two NMOS transistors in a CMOS NOR gate are connected in parallel. The worst case current to drive the output low happens when only one of these transistors is turned "ON". Thus each transistor has to have the same dimensions as the NMOS transistor in the inverter, namely  $\frac{W_{a}}{L_{a}} = 2$ .

The two PMOS transistors are connected in series. If each of these transistors had the ratio  $\frac{W_p}{L_p}$ , then the two transistors could be thought of as one transistor with a  $\frac{W_p}{2L_p}$  ratio. Thus each PMOS transistor must be made twice as wide as that in the inverter, namely  $\frac{W_n}{L_n} = 8$ .

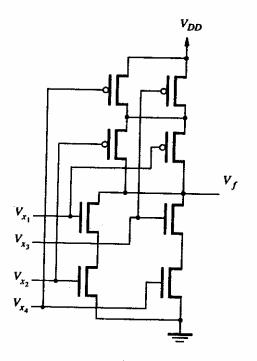

- 3.33. The worst case path in the PMOS network contains two transistors in series. Thus each PMOS transistor must be twice as wide the transistors in the inverter. The worst case path in the NMOS network also contains two transistors in series. Similarly, each NMOS transistor must be twice as wide as those in the inverter.

- 3.34. The worst case PMOS path contains three transistors in series so each transistor must be three times as wide as the PMOS transistors in the inverter. The worst case NMOS path contains two transistors in series. Thus the NMOS transistors must be two times as wide.

- 3.35. (a) The current flowing through the inverter is equal to the current flowing through the PMOS transistor. We shall assume that the PMOS transistor is operating in the saturation region.

$$I_{stat} = \frac{1}{2} k'_p \frac{W_p}{L_p} (V_{GS} - V_{Tp})^2$$

=  $120 \frac{\mu A}{V^2} \times ((3.5 V - 5 V) + 1 V)^2 = 30 \mu A$

(b) The current flowing through the NMOS transistor is equal to the static current  $I_{stat}$ . Assume that the NMOS transistor is operating in the triode region.

$$I_{stat} = k'_{n} \frac{W_{n}}{L_{n}} \left[ (V_{GS} - V_{Tn}) V_{DS} - \frac{1}{2} V_{DS}^{2} \right]$$

30 \mu A = 240 \frac{\mu A}{V^{2}} \times \left[ 2.5 \mathbf{V} \times V\_{f} - \frac{1}{2} V\_{f}^{2} \right]

1 = 20 V\_{f} - 4 V\_{f}^{2}

Solving this quadratic equation yields  $V_f = 0.05$  V. Note that the output voltage  $V_f$  satisfies the assumption that the PMOS transistor is operating in the saturation region while the NMOS transistor is operating in the triode region. (c) The static power dissipated in the inverter is

$$P_S = I_{stat} V_{DD} = 30 \,\mu\text{A} \times 5 \,\text{V} = 150 \,\mu\text{W}$$

(d) The static power dissipated by 250,000 inverters.

$$250,000 \times P_{\theta} = 37.5 \,\mathrm{W}$$

3 37.

3.36.

3.39.

3.38.

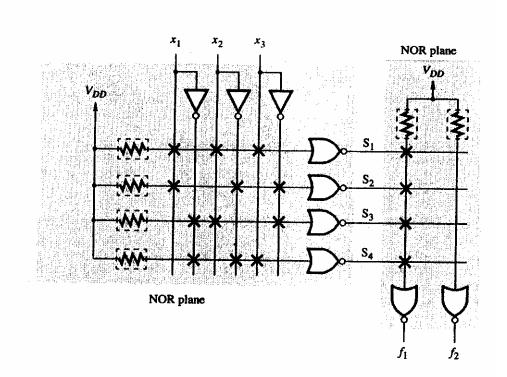

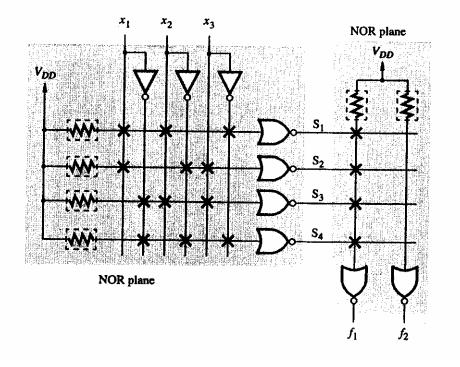

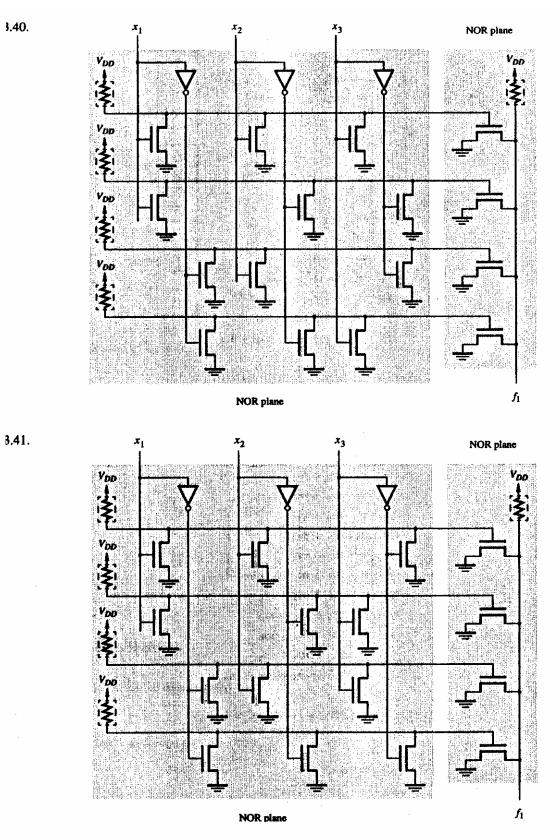

3.40.

3.42.

| $f_2$ | = | $m_1$                   |

|-------|---|-------------------------|

| $f_2$ | = | $m_2$                   |

| $f_2$ | = | $m_4$                   |

| $f_2$ | = | $m_7$                   |

| $f_2$ | = | $m_1 + m_2$             |

| $f_2$ | Ξ | $m_1 + m_4$             |

| $f_2$ | = | $m_1 + m_7$             |

| $f_2$ | = | $m_2 + m_4$             |

| $f_2$ | = | $m_2 + m_7$             |

| $f_2$ | = | $m_4 + m_7$             |

| $f_2$ | = | $m_1 + m_2 + m_4$       |

| $f_2$ | = | $m_1 + m_2 + m_7$       |

| $f_2$ | = | $m_1 + m_4 + m_7$       |

| $f_2$ | = | $m_2 + m_4 + m_7$       |

| $f_2$ | = | $m_1 + m_2 + m_4 + m_7$ |

3.43.

| $f_2$ | Ξ  | $m_0$                   |

|-------|----|-------------------------|

| $f_2$ | =  | $m_3$                   |

| $f_2$ | Ξ  | $m_5$                   |

| ∮₂    | Ξ  | $m_6$                   |

| $f_2$ | =  | $m_0 + m_3$             |

| $f_2$ | =  | $m_0 + m_5$             |

| $f_2$ | =  | $m_0 + m_6$             |

| $f_2$ | == | $m_3 + m_4$             |

| $f_2$ | =  | $m_3 + m_6$             |

| $f_2$ | Ξ  | $m_5 + m_6$             |

| $f_2$ | =  | $m_0 + m_3 + m_5$       |

| $f_2$ | Ξ  | $m_0 + m_3 + m_6$       |

| $f_2$ | =  | $m_0 + m_5 + m_6$       |

| $f_2$ | =  | $m_3 + m_5 + m_6$       |

| $f_2$ | =  | $m_0 + m_3 + m_5 + m_6$ |

|       |    |                         |

3.45. The canonical SOP for f is

$$f = \overline{x}_1 x_2 \overline{x}_3 + \overline{x}_1 x_2 x_3 + x_1 \overline{x}_2 \overline{x}_3 + x_1 x_2 \overline{x}_3 + x_1 x_2 x_3$$

This expression can be manipulated into

$$f = \overline{x}_1 x_2 + x_1 \overline{x}_3 + x_1 x_2$$

=  $x_2 + x_1 \overline{x}_3$

The circuit is

3.46. The canonical SOP for f is

$$f = x_1 x_2 x_4 + x_2 x_3 \overline{x}_4 + \overline{x}_1 \overline{x}_2 \overline{x}_3$$

This expression can be manipulated into

$$f = x_2 \cdot (x_1 x_4 + x_3 \overline{x}_4) + \overline{x}_2 \cdot (\overline{x}_1 \overline{x}_3)$$

Using functional decomposition we have

$$f = x_2 f_1 + \overline{x}_2 f_2$$

where

$$f_1 = x_1 x_4 + x_3 \overline{x}_4$$

$$f_2 = \overline{x}_1 \overline{x}_3$$

1.44.

The circuit is

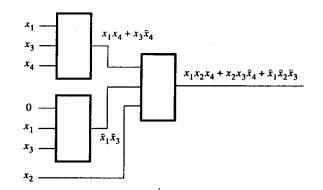

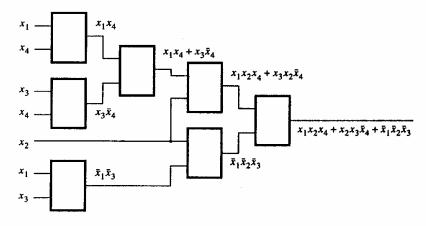

#### 3.47. The canonical SOP for f is

$$f = x_1 x_2 x_4 + x_2 x_3 \overline{x}_4 + \overline{x}_1 \overline{x}_2 \overline{x}_3$$

$$f = x_2 \cdot (x_1 x_4 + x_3 \overline{x}_4) + \overline{x}_2 \cdot (\overline{x}_1 \overline{x}_3)$$

Using functional decomposition we have

$$f = x_2 f_1 + \overline{x}_2 f_2$$

where

$$f_1 = x_1 x_4 + x_3 \overline{x}_4$$

$$f_2 = \overline{x}_1 \overline{x}_3$$

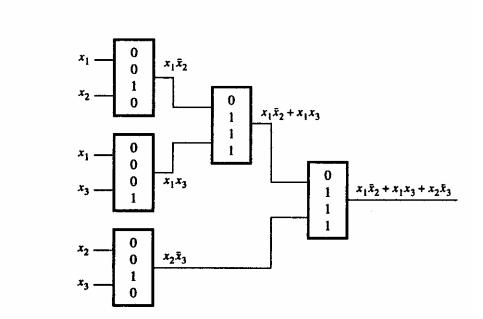

The function  $f_1$  requires one 2-LUT, while  $f_2$  requires three 2-LUTs. We then need three additional 3-LUTs to realize f, as illustrated in the circuit

3.48.

$$g = \overline{x}_2 x_3$$

$$h = x_1$$

$$j = x_2$$

$$k = x_3$$

```

|3.53. LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

ENTITY prob3_53 IS

PORT (x1, x2, x3, x4, x5, x6, x7 : IN STD_LOGIC ;

f : OUT STD_LOGIC ) ;

END prob3_53 ;

ARCHITECTURE LogicFunc OF prob3_53 IS

BEGIN

f <= (x1 \text{ AND } x3 \text{ AND NOT } x6) \text{ OR}

(x1 \text{ AND } x4 \text{ AND } x5 \text{ AND NOT } x6) \text{ OR}

(x2 \text{ AND } x3 \text{ AND } x7) \text{ OR}

(x2 \text{ AND } x4 \text{ AND } x5 \text{ AND } x7) ;

END LogicFunc ;

```

- 3.54. The circuit in Figure P3.10 is a two-input XOR gate. Since NMOS transistors are used only to pass logic 0 and PMOS transistors are used only to pass logic 1, the circuit does nor suffer from any major drawbacks.

- 3.55. The circuit in Figure P3.11 is a two-input XOR gate. This circuit has two drawbacks: when both inputs are 0 the PMOS transistor must drive f to 0, resulting in  $f = V_T$  volts. Also, when  $x_1 = 1$  and  $x_2 = 0$ , the NMOS transistor must drive the output high, resulting in  $f = V_{DD} V_T$ .

Thank you, Abe

Please report any mistake to the instructor.

## **Chapter 4**

- 4.1. SOP form:  $f = \overline{x}_1 x_2 + \overline{x}_2 x_3$ POS form:  $f = (\overline{x}_1 + \overline{x}_2)(x_2 + x_3)$

- 4.2. SOP form:  $f = x_1\overline{x}_2 + x_1x_3 + \overline{x}_2x_3$ POS form:  $f = (x_1 + x_3)(x_1 + \overline{x}_2)(\overline{x}_2 + x_3)$

- 4.3. SOP form:  $f = \overline{x}_1 x_2 x_3 \overline{x}_4 + x_1 x_2 \overline{x}_3 x_4 + \overline{x}_2 x_3 x_4$ POS form:  $f = (\overline{x}_1 + x_4)(x_2 + x_3)(\overline{x}_2 + \overline{x}_3 + \overline{x}_4)(x_2 + x_4)(x_1 + x_3)$

- 4.4. SOP form:  $f = \overline{x}_2 \overline{x}_3 + \overline{x}_2 \overline{x}_4 + x_2 x_3 x_4$ POS form:  $f = (\overline{x}_2 + x_3)(x_2 + \overline{x}_3 + \overline{x}_4)(\overline{x}_2 + x_4)$

- 4.5. SOP form:  $f = \overline{x}_3 \overline{x}_5 + \overline{x}_3 x_4 + x_2 x_4 \overline{x}_5 + \overline{x}_1 x_3 \overline{x}_4 x_5 + x_1 x_2 \overline{x}_4 x_5$ POS form:  $f = (\overline{x}_3 + x_4 + x_5)(\overline{x}_3 + \overline{x}_4 + \overline{x}_5)(x_2 + \overline{x}_3 + \overline{x}_4)(x_1 + x_3 + x_4 + \overline{x}_5)(\overline{x}_1 + x_2 + x_4 + \overline{x}_5)$

- 4.6. SOP form:  $f = \overline{x}_2 x_3 + \overline{x}_1 x_5 + \overline{x}_1 x_3 + \overline{x}_3 \overline{x}_4 + \overline{x}_2 x_5$ POS form:  $f = (\overline{x}_1 + \overline{x}_2 + \overline{x}_3)(\overline{x}_1 + \overline{x}_2 + \overline{x}_4)(x_3 + \overline{x}_4 + x_5)$

- 4.7. SOP form:  $f = x_3 \overline{x}_4 \overline{x}_5 + \overline{x}_3 \overline{x}_4 x_5 + x_1 x_4 x_5 + x_1 x_2 x_4 + x_3 x_4 x_5 + \overline{x}_2 x_3 x_4 + x_2 \overline{x}_3 x_4 \overline{x}_5$ POS form:  $f = (x_3 + x_4 + x_5)(\overline{x}_3 + x_4 + \overline{x}_5)(x_1 + \overline{x}_2 + \overline{x}_3 + \overline{x}_4 + x_5)$

4.8.

$$f = \sum m(0,7)$$

$f = \sum m(1,6)$

$f = \sum m(2,5)$

$f = \sum m(0,1,6)$

$f = \sum m(0,2,5)$

etc.

- $4.9. \ f = x_1 x_2 x_3 + x_1 x_2 x_4 + x_1 x_3 x_4 + x_2 x_3 x_4$

- 4.10. SOP form:  $f = x_1 x_2 \overline{x}_3 + x_1 \overline{x}_2 x_4 + x_1 x_3 \overline{x}_4 + \overline{x}_1 x_2 x_3 + \overline{x}_1 x_3 x_4 + x_2 \overline{x}_3 x_4$ POS form:  $f = (x_1 + x_2 + x_3)(x_1 + x_2 + x_4)(x_1 + x_3 + x_4)(x_2 + x_3 + x_4)(\overline{x}_1 + \overline{x}_2 + \overline{x}_3 + \overline{x}_4)$ The POS form has lower cost.

- 4.11. The statement is false. As a counter example consider  $f(x_1, x_2, x_3) = \sum m(0, 5, 7)$ . Then, the minimum-cost SOP form  $f = x_1x_3 + \overline{x}_1\overline{x}_2\overline{x}_3$  is unique. But, there are two minimum-cost POS forms:  $f = (x_1 + \overline{x}_3)(\overline{x}_1 + x_3)(x_1 + \overline{x}_2)$  and  $f = (x_1 + \overline{x}_3)(\overline{x}_1 + x_3)(\overline{x}_2 + x_3)$

4.12. If each circuit is implemented separately:  $f = \overline{x}_1 \overline{x}_4 + \overline{x}_1 x_2 x_3 + x_1 \overline{x}_2 x_4 \quad \text{Cost} = 15$   $g = \overline{x}_1 \overline{x}_3 \overline{x}_4 + \overline{x}_2 x_3 \overline{x}_4 + x_1 \overline{x}_3 x_4 + x_1 x_2 x_4 \quad \text{Cost} = 21$ In a combined circuit:

$f = \overline{x}_2 x_3 \overline{x}_4 + \overline{x}_1 \overline{x}_3 \overline{x}_4 + x_1 \overline{x}_2 \overline{x}_3 x_4 + \overline{x}_1 x_2 x_3$   $g = \overline{x}_2 x_3 \overline{x}_4 + \overline{x}_1 \overline{x}_3 \overline{x}_4 + x_1 \overline{x}_2 \overline{x}_3 x_4 + x_1 x_2 x_4$ The first 3 product terms are shared, hence the total cost is 31.

4.13. If each circuit is implemented separately:  $f = \overline{x}_1 x_2 x_4 + x_2 x_4 x_5 + x_3 \overline{x}_4 \overline{x}_5 + \overline{x}_1 \overline{x}_2 \overline{x}_4 x_5 \quad \text{Cost} = 22$   $g = \overline{x}_3 \overline{x}_5 + \overline{x}_4 \overline{x}_5 + \overline{x}_1 \overline{x}_2 \overline{x}_4 + \overline{x}_1 x_2 x_4 + x_2 x_4 x_5 \quad \text{Cost} = 24$

In a combined circuit:  $f = \overline{x}_1 x_2 x_4 + x_2 x_4 x_5 + x_3 \overline{x}_4 \overline{x}_5 + \overline{x}_1 \overline{x}_2 \overline{x}_4 x_5$   $g = \overline{x}_1 x_2 x_4 + x_2 x_4 x_5 + x_3 \overline{x}_4 \overline{x}_5 + \overline{x}_1 \overline{x}_2 \overline{x}_4 x_5 + \overline{x}_3 \overline{x}_5$

The first 4 product terms are shared, hence the total cost is 31. Note that in this implementation  $f \subseteq g$ , thus g can be realized as  $g = f + \overline{x}_3 \overline{x}_5$ , in which case the total cost is lowered to 28.

4.14.  $f = (x_3 \uparrow g) \uparrow ((g \uparrow g) \uparrow x_4)$  where  $g = (x_1 \uparrow (x_2 \uparrow x_2)) \uparrow ((x_1 \uparrow x_1) \uparrow x_2)$

- 4.15.  $\overline{f} = (((x_3 \downarrow x_3) \downarrow g) \downarrow ((g \downarrow g) \downarrow (x_4 \downarrow x_4)))$ , where  $g = ((x_1 \downarrow x_1) \downarrow x_2) \downarrow (x_1 \downarrow (x_2 \downarrow x_2))$ . Then,  $f = \overline{f} \downarrow \overline{f}$ .

- 4.16.  $f = (g \uparrow k) \uparrow ((g \uparrow g) \uparrow (k \uparrow k))$ , where  $g = (x_1 \uparrow x_1) \uparrow (x_2 \uparrow x_2) \uparrow (x_5 \uparrow x_5)$ and  $k = (x_3 \uparrow (x_4 \uparrow x_4)) \uparrow ((x_3 \uparrow x_3) \uparrow x_4)$

- 4.17.  $\overline{f} = (g \downarrow k) \downarrow ((g \downarrow g) \downarrow (k \downarrow k))$ , where  $g = x_1 \downarrow x_2 \downarrow x_5$ and  $k = ((x_3 \downarrow x_6) \downarrow x_4) \downarrow (x_3 \downarrow (x_4 \downarrow x_4))$ . Then,  $f = \overline{f} \downarrow \overline{f}$ .

4.18.

$$f = \overline{x}_1(x_2 + x_3)(x_4 + x_5) + x_1(\overline{x}_2 + x_3)(\overline{x}_4 + x_5)$$

4.19.  $f = x_1\overline{x}_3\overline{x}_4 + x_2\overline{x}_3\overline{x}_4 + x_1x_3x_4 + x_2x_3x_4 = (x_1 + x_2)\overline{x}_3\overline{x}_4 + (x_1 + x_2)x_3x_4$ This requires 2 OR and 2 AND gates.

4.20.  $f = x_1 \cdot g + \overline{x}_1 \cdot \overline{g}$ , where  $g = \overline{x}_3 x_4 + x_3 \overline{x}_4$

- 4.21  $f = g \cdot h + \overline{g} \cdot \overline{h}$ , where  $g = x_1 x_2$  and  $h = x_3 + x_4$

- 4.22. Let D(0, 20) be 0 and D(15, 26) be 1. Then decomposition yields:  $g = x_5(\overline{x}_1 + x_2)$   $f = (\overline{x}_3\overline{x}_4 + x_3x_4)g + \overline{x}_3x_4\overline{g} = x_3x_4g + \overline{x}_3\overline{x}_4g + \overline{x}_3x_4\overline{g}$ Cost = 9 + 18 = 27

The optimal SOP form is:  $f = \overline{x}_3 x_4 \overline{x}_5 + \overline{x}_1 x_3 x_4 x_5 + x_1 \overline{x}_2 \overline{x}_3 x_4 + \overline{x}_1 \overline{x}_3 \overline{x}_4 x_5 + x_2 \overline{x}_3 \overline{x}_4 x_5 + x_2 x_3 x_4 x_5$ Cost = 7 + 29 = 36

4.23. Note that  $X # Y = X \cdot \overline{Y}$ . Therefore,

$(A \cdot B) \# C = A \cdot B \cdot \overline{c}$  $(A \# C) \cdot (B \# C) = A \cdot \overline{C} \cdot B \cdot \overline{C}$  $= A \cdot B \cdot \overline{C}$

Similarly,

$$(A+B)\#C = (A+B)\cdot\overline{C}$$

$$= A\cdot\overline{C}+B\cdot\overline{C}$$

$$(A\#C)+(B\#C) = A\cdot\overline{C}+B\cdot\overline{C}$$

- 4.24. The initial cover is  $C^0 = \{0000, 0011, 0100, 0101, 0111, 1000, 1001, 1111\}$ . Using the \*-product get the prime implicants  $P = \{00x0, 0x00, x000, 010x, 01x1, 100x, x111\}$ . The minimum cover is  $C_{minimum} = \{00x0, 010x, 100x, x111\}$ , which corresponds to  $f = \overline{x}_1 \overline{x}_2 \overline{x}_4 + \overline{x}_1 x_2 \overline{x}_3 + x_1 \overline{x}_2 \overline{x}_3 + x_2 x_3 x_4$ .

- 4.25. The initial cover is  $C^0 = \{0x0x0, 110xx, x1101, 1001x, 11110, 01x10, 0x011\}$ . Using the \*-product get the prime implicants  $P = \{0x0x0, xx01x, x1x10, 110xx, x10x0, 11x01, x1101\}$ . The minimum cover is  $C_{minimum} = \{0x0x0, xx01x, x1x10, 110xx, x1101\}$ , which corresponds to  $f = \overline{x_1}\overline{x_3}\overline{x_5} + \overline{x_3}x_4 + x_2x_4\overline{x_5} + x_1x_2\overline{x_3} + x_2x_3\overline{x_4}x_5$ .

- 4.26. The initial cover is  $C^0 = \{00x0, 100x, x010, 1111, 00x1, 011x\}$ . Using the \*-product get the prime implicants  $P = \{00xx, 0x1x, x00x, x0x0, x111\}$ . The minimum-cost cover is  $C_{minimum} = \{x00x, x0x0, x111\}$ , which corresponds to  $f = \overline{x}_2 \overline{x}_3 + \overline{x}_2 \overline{x}_4 + x_2 x_3 x_4$ .

- 4.27. Expansion of  $\overline{x}_1 \overline{x}_2 \overline{x}_3$  gives  $\overline{x}_1$ . Expansion of  $\overline{x}_1 \overline{x}_2 x_3$  gives  $\overline{x}_1$ . Expansion of  $\overline{x}_1 x_2 \overline{x}_3$  gives  $\overline{x}_1$ . Expansion of  $x_1 x_2 x_3$  gives  $x_2 x_3$ . The set of prime implicants comprises  $\overline{x}_1$  and  $x_2 x_3$ .

- 4.28. Expansion of  $\overline{x}_1 x_2 \overline{x}_3 x_4$  gives  $x_2 \overline{x}_3 x_4$  and  $\overline{x}_1 x_2 x_4$ . Expansion of  $x_1 x_2 \overline{x}_3 x_4$  gives  $x_2 \overline{x}_3 x_4$ . Expansion of  $x_1 x_2 x_3 \overline{x}_4$  gives  $x_3 \overline{x}_4$ . Expansion of  $\overline{x}_1 x_2 x_3$  gives  $\overline{x}_1 x_3$ . Expansion of  $\overline{x}_2 x_3$  gives  $\overline{x}_2 x_3$ . The set of prime implicants comprises  $x_2 \overline{x}_3 x_4$ ,  $\overline{x}_1 x_2 x_4$ ,  $x_3 \overline{x}_4$ ,  $\overline{x}_1 x_3$ , and  $\overline{x}_2 x_3$ .

4.29. Representing both functions in the form of Karnaugh map, it is easy to show that f = g. The minimum cost SOP expression is

$f = g = \overline{x}_2 \overline{x}_3 \overline{x}_5 + \overline{x}_2 x_3 \overline{x}_4 + x_1 x_3 x_4 + x_1 x_2 x_4 x_5.$

4.30. The cost of the circuit in Figure P4.2 is 11 gates and 30 inputs, for a total of 41. The functions implemented by the circuit can also be realized as

$f = \bar{x}_1 \bar{x}_2 \bar{x}_4 + x_2 \bar{x}_3 \bar{x}_4 + \bar{x}_1 x_3 x_4 + x_1 x_4$  $g = \bar{x}_1 \bar{x}_2 \bar{x}_4 + x_2 \bar{x}_3 \bar{x}_4 + \bar{x}_1 x_3 x_4 + \bar{x}_2 x_4 + x_3 \bar{x}_4$

The first three product terms in f and g are the same; therefore, they can be shared. Then, the cost of implementing f and g is 8 gates and 24 inputs, for a total of 32.

4.31. The cost of the circuit in Figure P4.3 is 11 gates and 26 inputs, for a total of 37. The functions implemented by the circuit can also be realized as

$f = (\overline{x}_2 \uparrow x_4) \uparrow (\overline{x}_1 \uparrow x_2 \uparrow x_3) \uparrow (x_1 \uparrow \overline{x}_2 \uparrow x_3) \uparrow (\overline{x}_2 \uparrow \overline{x}_3)$  $g = (\overline{x}_2 \uparrow x_4) \uparrow (\overline{x}_1 \uparrow x_2 \uparrow x_3) \uparrow (x_1 \uparrow \overline{x}_2 \uparrow x_3) \uparrow (\overline{x}_1 \uparrow \overline{x}_1)$

The first three NAND terms in f and g are the same; therefore, they can be shared. Then, the cost of implementing f and g is 7 gates and 20 inputs, for a total of 27.

## **Chapter 5**

- 5.1. (a) 478 (b) 743 (c) 2025 (d) 41567 (e) 61680

- 5.2. (a) 478 (b) -280

- (c) -1

- 5.3. (a) 478 (b) -281 (c) -2

- 5.4. The numbers are represented as follows:

| Decimal | Sign and Magnitude | 1's Complement | 2's Complement |

|---------|--------------------|----------------|----------------|

| 73      | 000001001001       | 000001001001   | 000001001001   |

| 1906    | 011101110010       | 011101110010   | 011101110010   |

| -95     | 100001011111       | 111110100000   | 111110100001   |

| -1630   | 111001011110       | 100110100001   | 100110100010   |

5.5. The results of the operations are:

| (a): | 00110110<br>+01000101<br>01111011        | 54<br><u>+69</u><br>123 | (b): | 01110101<br><u>+11011110</u><br>01010011 | $   \begin{array}{r}     117 \\     \underline{-34} \\     83   \end{array} $ | (c):          | 11011111<br>+10111000<br>10010111        | (-33)<br><u>+(-72)</u><br>(-105) |

|------|------------------------------------------|-------------------------|------|------------------------------------------|-------------------------------------------------------------------------------|---------------|------------------------------------------|----------------------------------|

| (d): | 00110110<br><u>-00101011</u><br>00001011 | 54<br><u>-43</u><br>11  | (e): | 01110101<br><u>-11010110</u><br>10011111 | (117)<br><u>-(- 42)</u><br>(159)                                              | ( <i>f</i> ): | 11010011<br><u>-11101100</u><br>11100111 | (-45)<br><u>-(-20)</u><br>(-25)  |

Arithmetic overflow occurs in example e; note that the pattern 10011111 represents -97 rather than +159.

5.6. The associativity of the XOR operation can be shown as follows:

$$\begin{aligned} x \oplus (y \oplus z) &= x \oplus (\overline{y}z + y\overline{z}) \\ &= \overline{x}(\overline{y}z + y\overline{z}) + x(\overline{y} \cdot \overline{z} + yz) \\ &= \overline{x} \cdot \overline{y}z + \overline{x}y\overline{z} + x\overline{y} \cdot \overline{z} + xyz \end{aligned}$$

$$(x \oplus y) \oplus z &= (\overline{x}y + x\overline{y}) \oplus z \\ &= (\overline{x} \cdot \overline{y} + xy)z + (\overline{x}y + x\overline{y})\overline{z} \\ &= \overline{x} \cdot \overline{y}z + xyz + \overline{x}y\overline{z} + x\overline{y} \cdot \overline{z} \end{aligned}$$

The two SOP expressions are the same.

5.7. In the circuit of Figure 5.5b, we have:

$$s_i = (x_i \oplus y_i) \oplus c_i$$

=  $x_i \oplus y_i \oplus c_i$

$$c_{i+1} = (x_i \oplus y_i)c_i + x_iy_i$$

=  $(\overline{x}_iy_i + x_i\overline{y}_i)c_i + x_iy_i$

=  $\overline{x}_iy_ic_i + x_i\overline{y}_ic_i + x_iy_i$

=  $y_ic_i + x_ic_i + x_iy_i$

The expressions for  $s_i$  and  $c_{i+1}$  are the same as those derived in Figure 5.4b.

- 5.8. We will give a descriptive proof for ease of understanding. The 2's complement of a given number can be found by adding 1 to the 1's complement of the number. Suppose that the number has k 0s in the least-significant bit positions,  $b_{k-1} \dots b_0$ , and it has  $b_k = 1$ . When this number is converted to its 1's complement, each of these k bits has the value 1. Adding 1 to this string of 1s produces  $b_k b_{k-1} b_{k-2} \dots b_0 = 100 \dots 0$ . This result is equivalent to copying the k 0s and the first 1 (in bit position  $b_k$ ) encountered when the number is scanned from right to left. Suppose that the most-significant n-k bits,  $b_{n-1}b_{n-2} \dots b_k$ , have some pattern of 0s and 1s, but  $b_k = 1$ . In the 1's complement this pattern will be complemented in each bit position, which will include  $b_k = 0$ . Now, adding 1 to the entire *n*-bit number will make  $b_k = 1$ , but no further carries will be generated; therefore, the complemented bits in positions  $b_{n-1}b_{n-2} \dots b_{k+1}$  will remain unchanged.

- 5.9. Construct the truth table

| $x_{n-1}$ | <i>y</i> n−1 | Cn-1 | Cn | $s_{n-1}$ (sign bit) | Overflow |

|-----------|--------------|------|----|----------------------|----------|

| 0         | 0            | 0    | 0  | 0                    | 0        |

| 0         | 0            | 1    | 0  | - 1                  | . 1      |

| 0         | 1            | 0    | 0  | 1                    | 0        |

| 0         | 1            | 1    | 1  | 0                    | 0        |

| 1         | 0            | 0    | 0  | 1                    | 0        |

| 1         | 0            | 1    | 1  | 0                    | 0        |

| 1         | 1            | 0    | 1  | 0                    | 1        |

| 1         | 1            | 1    | 1  | 1                    | 0        |

Note that overflow cannot occur when two numbers with opposite signs are added. From the truth table the overflow expression is

$Overflow = \overline{c}_n c_{n-1} + c_n \overline{c}_{n-1} = c_n \oplus c_{n-1}$

5.10. Since  $s_k = x_k \oplus y_k \oplus c_k$ , it follows that

$$\begin{aligned} x_k \oplus y_k \oplus s_k &= (x_k \oplus y_k) \oplus (x_k \oplus y_k \oplus c_k) \\ &= (x_k \oplus y_k) \oplus (x_k \oplus y_k) \oplus c_k \\ &= 0 \oplus c_k \\ &= c_k \end{aligned}$$

- 5.11. Yes, it works. The NOT gate that produces  $c_i$  is not needed in stages where i > 0. The drawback is "poor" propagation of  $\bar{c}_i = 1$  through the topmost NMOS transistor. The positive aspect is fewer transistors needed to produce  $\bar{c}_{i+1}$ .

- 5.12. From Expression 5.4, each  $c_i$  requires *i* AND gates and one OR gate. Therefore, to determine all  $c_i$  signals we need  $\sum_{i=1}^{n} (i+1) = (n^2 + 3n)/2$  gates. In addition to this, we need 3n gates to generate all g, p, and s functions. Therefore, a total of  $(n^2 + 9n)/2$  gates are needed.

- 5.13. 84 gates.

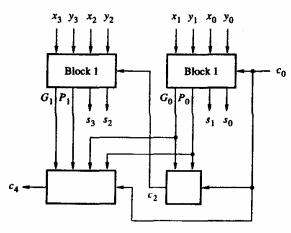

- 5.14. The circuit for a 4-bit version of the adder based on the hierarchical structure in Figure 5.18 is constructed as follows:

Blocks 0 and 1 have the structure similar to the circuit in Figure 5.16. The overall circuit is given by the expressions

$$p_i = x_i + y_i$$

$$g_i = x_i y_i$$

$$P_0 = p_1 p_0$$

$$G_0 = g_1 + p_1 g_0$$

- $P_{1} = p_{3}p_{2}$   $G_{1} = g_{3} + p_{3}g_{2}$   $c_{2} = G_{0} + P_{0}c_{0}$   $c_{4} = G_{1} + P_{1}G_{0} + P_{1}P_{0}c_{0}$

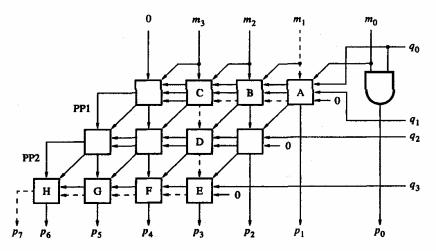

- 5.15. The longest path, which causes the critical delay, is from the inputs  $m_0$  and  $m_1$  to the output  $p_7$ , indicated by the dashed path in the following copy of Figure 5.33a:

Propagation through the block A involves one gate delay in the AND gate shown in Figure 5.33b and two gate delays to generate the carry-out in the full-adder. Then, in each of the blocks B, C, D, E, F, G, and H, two more gate delays are needed to generate the carry-out signals in the circuits depicted by Figure 5.33c. Therefore, the total delay along the critical path is 17 gate delays.

```

5.16. (a) LIBRARY iece;

```

```

USE ieee.std_logic_1164.all ;

ENTITY row0 IS

PORT ( q0, q1, cin, mk, mkp1 : IN STD_LOGIC ;

s, cout : OUT STD_LOGIC );

END row0;

ARCHITECTURE LogicFunc OF row0 IS

SIGNAL a0, a1 : STD_LOGIC ;

BEGIN

a0 <= q0 AND mkp1 ;

a1 <= q1 AND mk ;

s <= cin XOR a0 XOR a1 ;

cout <= (cin AND a0) OR (cin AND a1) OR (a0 AND a1) ;

END LogicFunc ;

```

```

(b) LIBRARY iece :

USE ieee.std_logic_1164.all;

ENTITY row1 IS

PORT (qj, cin, mk, BitPPi : IN STD_LOGIC ;

s, cout

: OUT STD_LOGIC);

END row1;

ARCHITECTURE LogicFunc OF row1 IS

SIGNAL a0 : STD_LOGIC ;

BEGIN

a0 \le qj AND mk;

s <= cin XOR a0 XOR BitPPi :</p>

cout <= (cin AND a0) OR (cin AND BitPPi) OR (a0 AND BitPPi);

END LogicFunc :

(c) LIBRARY ieee;

USE ieee.std_logic_1164.all :

ENTITY mult4x4 IS

PORT (cin : IN STD_LOGIC ;

M, Q : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Ρ

: OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );

END mult4x4 ;

ARCHITECTURE Structure OF mult4x4 IS

COMPONENT row0

PORT (q0, q1, cin, mk, mkp1 : IN STD_LOGIC :

s. cout

: OUT STD_LOGIC);

END COMPONENT :

COMPONENT row1

PORT (qj, cin, mk, BitPPi : IN STD_LOGIC;

s, cout

: OUT STD_LOGIC);

END COMPONENT ;

SIGNAL PP1 : STD_LOGIC_VECTOR(5 DOWNTO 2);

SIGNAL PP2 : STD_LOGIC_VECTOR(6 DOWNTO 3);

SIGNAL Crow0, Crow1, Crow2: STD_LOGIC_VECTOR(1 TO 3);

BEGIN

P(0) \le Q(0) \text{ AND } M(0);

row0_1: row0 PORT MAP ( Q(0), Q(1), cin, M(0), M(1), P(1), Crow0(1) );

row0_2: row0 PORT MAP ( Q(0), Q(1), Crow0(1), M(1), M(2), PP1(2), Crow0(2) );

row0_3: row0 PORT MAP (Q(0), Q(1), Crow0(2), M(2), M(3), PP1(3), Crow0(3));

row0_4: row0 PORT MAP (Q(0), Q(1), Crow0(3), M(3), cin, PP1(4), PP1(5));

row1_2: row1 PORT MAP (Q(2), cin, M(0), PP1(2), P(2), Crow1(1));

row1_3: row1 PORT MAP (Q(2), Crow1(1), M(1), PP1(3), PP2(3), Crow1(2));

row1_4: row1 PORT MAP ( Q(2), Crow1(2), M(2), PP1(4), PP2(4), Crow1(3) );

row1_5: row1 PORT MAP ( Q(2), Crow1(3), M(3), PP1(5), PP2(5), PP2(6) );

row2_3: row1 PORT MAP (Q(3), cin, M(0), PP2(3), P(3), Crow2(1));

row2_4: row1 PORT MAP (Q(3), Crow2(1), M(1), PP2(4), P(4), Crow2(2));

row2_5: row1 PORT MAP ( Q(3), Crow2(2), M(2), PP2(5), P(5), Crow2(3) );

row2_6: row1 PORT MAP ( Q(3), Crow2(3), M(3), PP2(6), P(6), P(7) );

END Structure ;

```

- 5.17. The code in Figure P5.2 represents a multiplier. It multiplies the lower two bits of *Input* by the upper two bits of *Input*, producing the four-bit *Output*. The style of code is poor, because it is not readily apparent what is being described.

- 5.18. Let  $Y = y_3y_2y_1y_0$  be the 9's complement of the BCD digit  $X = x_3x_2x_1x_0$ . Then, Y is defined by the truth table

| X3 | 22 | z1 | xo | 3/3 | Y2 | Y1 | Yo |

|----|----|----|----|-----|----|----|----|

| 0  | 0  | 0  | 0  | 1   | 0  | 0  | 1  |

| 0  | 0  | 0  | 1  | 1   | 0  | 0  | 0  |

| 0  | 0  | 1  | 0  | 0   | 1  | 1  | 1  |

| 0  | 0  | 1  | 1  | 0   | 1  | 1  | 0  |

| 0  | 1  | 0  | 0  | 0   | 1  | 0  | 1  |

| 0  | 1  | 0  | 1  | 0   | 1  | 0  | 0  |

| 0  | 1  | 1  | 0  | 0   | 0  | 1  | 1  |

| 0  | 1  | 1  | 1  | 0   | 0  | 1  | 0  |

| 1  | 0  | 0  | 0  | 0   | 0  | 0  | 1  |

| 1  | 0  | 0  | 1  | 0   | 0  | 0  | 0  |

This gives

$y_0 = \overline{x}_0$   $y_1 = x_1$   $y_2 = \overline{x}_2 x_1 + x_2 \overline{x}_1$  $y_3 = \overline{x}_3 \overline{x}_2 \overline{x}_1$

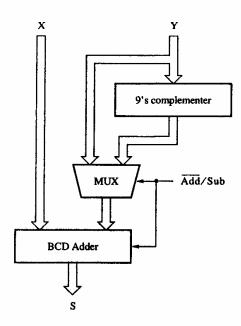

5.19. BCD subtraction can be performed using 10's complement representation, using an approach that is similar to 2's complement subtraction. Note that 10's and 2's complements are the radix complements in number systems where the radices are 10 and 2, respectively. Let X and Y be BCD numbers given in 10's complement representation, such that the sign (left-most) BCD digit is 0 for positive numbers and 9 for negative numbers. Then, the subtraction operation S = X - Y is performed by finding the 10's complement of Y and adding it to X, ignoring any carry-out from the sign-digit position.

For example, let X = 068 and Y = 043. Then, the 10's complement of Y is 957, and S' = 068 + 957 = 1025. Dropping the carry-out of 1 from the sign-digit position gives S = 025.

As another example, let X = 0.32 and Y = 0.43. Then, S = 0.32 + 9.57 = 9.89, which represents  $-1.1_{10}$ .

The 10's complement of Y can be formed by adding 1 to the 9's complement of Y. Therefore, a circuit that can add and subtract BCD operands can be designed as follows:

For the 9's complementer one can use the circuit designed in problem 5.18. The BCD adder is a circuit based on the approach illustrated in Figure 5.40.

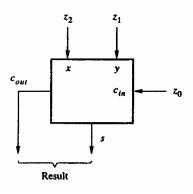

5.21. A full-adder circuit can be used, such that two of the bits of the number are connected as inputs x and y, while the third bit is connected as the carry-in. Then, the carry-out and sum bits will indicate how many input bits are equal to 1.

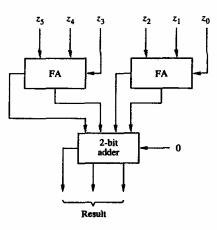

5.22. Using the approach explained in the solution to problem 5.21, the desired circuit can be built as follows:

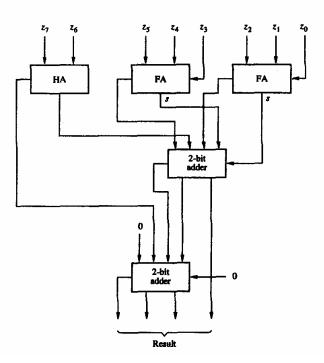

5.23. Using the approach explained in the solutions to problems 5.21 and 5.22, the desired circuit can be built as follows:

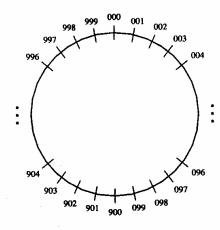

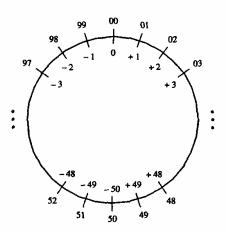

#### 5.24. The graphical representation is

For example, the addition -3 + (+5) = 2 involves starting at 997 (= -3) and going clockwise 5 numbers, which gives the result 002 (= +2). Similarly, the subtraction 4 - (+8) = -4 involves starting at 004 (= +4) and going counterclockwise 8 numbers, which gives the result 996 (= -4).

5.25. The ternary half-adder in Figure P5.3 can be defined using binary-encoded signals as follows:

|    | Ą  | ]          | 3  | Carry | Su         | ım         |

|----|----|------------|----|-------|------------|------------|

| a1 | ao | <b>b</b> 1 | bo | Cout  | <i>s</i> 1 | <i>8</i> 0 |

| 0  | 0  | 0          | 0  | 0     | 0          | 0          |

| 0  | 0  | 0          | 1  | 0     | 0          | 1          |

| 0  | 0  | 1          | 0  | 0     | 1          | 0          |

| 0  | 1  | 0          | 0  | 0     | 0          | 1          |

| 0  | 1  | 0          | 1  | 0     | 1          | 0          |

| 0  | 1  | 1          | 0  | 1     | 0          | 0          |

| 1  | 0  | 0          | 0  | 0     | 1          | 0          |

| 1  | 0  | 0          | 1  | 1     | 0          | 0          |

| 1  | 0  | 1          | 0  | 1     | 0          | 1          |

The remaining 7 (out of 16) valuations, where either  $a_1 = a_0 = 1$ , or  $b_1 = b_0 = 1$ , can be treated as don't care conditions. Then, the minimum cost expressions are:

$c_{out} = a_0b_1 + a_1b_1 + a_1b_0$   $s_1 = a_0b_0 + \overline{a}_1\overline{a}_0b_1 + a_1\overline{b}_1\overline{b}_0$  $s_0 = a_1b_1 + \overline{a}_1\overline{a}_0b_0 + a_0\overline{b}_1\overline{b}_0$  26. Ternary full-adder is defined by the truth table:

| Cin | Α | В                     | Cout        | Sum    |

|-----|---|-----------------------|-------------|--------|

| 0   | 0 | 0                     | 0           | 0      |

| 0   | 0 | 1                     | 0           | 1      |

| 0   | 0 |                       | 0<br>0<br>0 | 2      |

| 0   | 1 | 2<br>0<br>1<br>2<br>0 | 0           | 1      |

| 0   | 1 | 1                     | 0           | 2      |

| 0   | 1 | 2                     | 1           | 0      |

| 0   | 2 | 0                     | 0           | 2      |

| 0   | 2 | 1                     | 1           | 0      |

| 0   | 2 | 2<br>0                | 1           | 1      |

| 1   | 0 |                       | 0           | 1      |

| 1   | 0 | 1                     | 0           | 2      |

| 1   | 0 | 2                     |             | 2<br>0 |

| 1   | 1 | 0                     | 1<br>0      | 2<br>0 |

| 1   | 1 | 1                     | 1           | 0      |

| 1   | 1 | 2                     | 1           | 1      |

| 1   | 2 | 0                     | 1           | 1<br>0 |

| 1   | 2 | 1                     | 1           | 1      |

| 1   | 2 | 2                     | 1           | 2      |

Using binary-encoded signals for this full-adder gives the following truth table:

|     | 4              | <b>A</b>       | ]          | B          |      | S  | ım              |

|-----|----------------|----------------|------------|------------|------|----|-----------------|

| Cin | a <sub>1</sub> | a <sub>0</sub> | <b>b</b> 1 | <b>b</b> 0 | Cout | 81 | \$ <sub>0</sub> |

| 0   | 0              | 0              | 0          | 0          | 0    | 0  | 0               |

| 0   | 0              | 0              | 0          | 1          | 0    | 0  | 1               |

| 0   | 0              | 0              | 1          | 0          | 0    | 1  | 0               |

| 0   | 0              | 1              | 0          | 0          | 0    | 0  | 1               |

| 0   | 0              | 1              | 0          | 1          | 0    | 1  | 0               |

| 0   | 0              | 1              | 1          | 0          | 1    | 0  | 0               |

| 0   | 1              | 0              | 0          | 0          | 0    | 1  | 0               |

| 0   | 1              | 0              | 0          | 1          | 1    | 0  | 0               |

| 0   | 1              | 0              | 1          | 0          | 1    | 0  | 1               |

| 1   | 0              | 0              | 0          | 0          | 0    | 0  | 1               |

| 1   | 0              | 0              | 0          | 1          | 0    | 1  | 0               |

| 1   | 0              | 0              | 1          | 0          | 1    | 0  | 0               |

| 1   | 0              | 1              | 0          | 0          | 0    | 1  | 0               |

| 1   | 0              | 1              | 0          | 1          | 1    | 0  | 0               |

| 1   | 0              | 1              | 1          | 0          | 1    | 0  | 1               |

| 1   | 1              | 0              | 0          | 0          | 1    | 0  | 0               |

| 1   | 1              | 0              | 0          | 1          | 1    | 0  | 1               |

| 1   | 1              | 0              | 1          | 0          | 1    | 1  | 0               |

Treating the 14 (out of 32) valuations where either  $a_1 = a_0 = 1$  or  $b_1 = b_0 = 1$  as don't care conditions, leads to the minimum cost expressions

- $c_{out} = a_0b_1 + a_1b_0 + a_1b_1 + a_1c_{in} + b_1c_{in} + a_0b_0c_{in}$

- $s_1 = a_0 b_0 \bar{c}_{in} + \bar{a}_1 \bar{a}_0 b_1 \bar{c}_{in} + a_1 \bar{b}_1 \bar{b}_0 \bar{c}_{in} + a_1 b_1 c_{in} + \bar{a}_1 \bar{a}_0 b_0 c_{in} + a_0 \bar{b}_1 \bar{b}_0 c_{in}$

- $s_0 = a_1 b_1 \overline{c}_{in} + \overline{a}_1 \overline{a}_0 b_0 \overline{c}_{in} + a_0 \overline{b}_1 \overline{b}_0 \overline{c}_{in} + a_1 b_0 c_{in} + a_0 b_1 c_{in} + \overline{a}_1 \overline{a}_0 \overline{b}_1 \overline{b}_0 c_{in}$

- 5.27. The subtractions 26 27 = 99 and 18 34 = 84 make sense if the two-digit numbers 00 to 99 are interpreted so that the numbers 00 to 49 are positive integers from 0 to +49, while the numbers 50 to 99 are negative integers from -50 to -1. This scheme can be illustrated graphically as follows:

Thanks.

# Chapter 6

6.1.

6.2.

6.3.

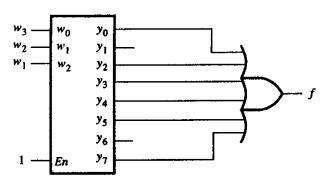

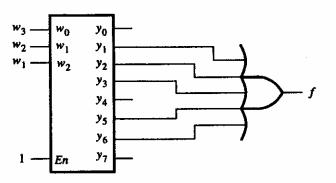

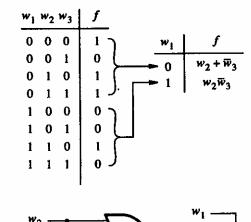

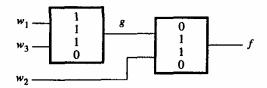

$w_1 w_2 w_3$ f 0 t 0 0 w<sub>1</sub> 0 0 1 0 ₩<sub>2</sub>₩<sub>3</sub> n 0 0 1 0  $w_2 + \overline{w}_3$ 0 -1 1 0 0 0 1 I 1 0 1 0 0 1 1 1 1 1 ł 1

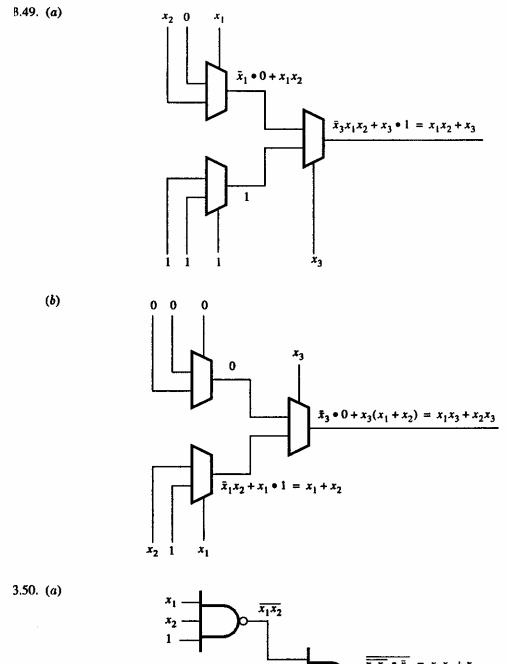

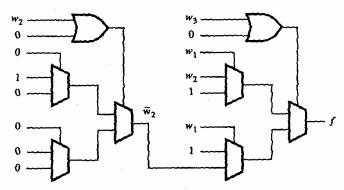

6.5. The function f can be expressed as

$f = \overline{w}_1 \overline{w}_2 \overline{w}_3 + \overline{w}_1 w_2 \overline{w}_3 + \overline{w}_1 w_2 w_3 + w_1 w_2 \overline{w}_3$

Expansion in terms of  $w_1$  produces

$$f = \overline{w}_1(w_2 + \overline{w}_3) + w_1(w_2\overline{w}_3)$$

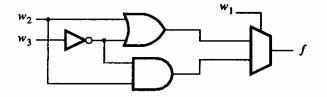

The corresponding circuit is

6.6. The function f can be expressed as

$$f = \overline{w}_1 \overline{w}_2 \overline{w}_3 + w_1 \overline{w}_2 \overline{w}_3 + w_1 w_2 \overline{w}_3 + w_1 w_2 w_3$$

Expansion in terms of  $w_2$  produces

$$f = \overline{w}_2(\overline{w}_3) + w_2(w_1)$$

The corresponding circuit is

6.4.

6.7. Expansion in terms of  $w_2$  gives

$f = \overline{w}_2(1 + \overline{w}_1\overline{w}_3 + w_1w_3) + w_2(\overline{w}_1\overline{w}_3 + w_1w_3)$  $= \overline{w}_1\overline{w}_2\overline{w}_3 + w_1\overline{w}_2w_3 + \overline{w}_2 + \overline{w}_1w_2\overline{w}_3 + w_1w_2w_3$

Further expansion in terms of  $w_1$  gives

$f = \overline{w}_1(w_2\overline{w}_3 + \overline{w}_2\overline{w}_3 + \overline{w}_2) + w_1(w_2w_3 + \overline{w}_2w_3 + \overline{w}_2)$  $= \overline{w}_1w_2\overline{w}_3 + \overline{w}_1\overline{w}_2\overline{w}_3 + \overline{w}_1\overline{w}_2 + w_1w_2w_3 + w_1\overline{w}_2w_3 + w_1\overline{w}_2$

Further expansion in terms of  $w_3$  gives

$f = \overline{w}_3(\overline{w}_1w_2 + \overline{w}_1\overline{w}_2 + \overline{w}_1\overline{w}_2 + w_1\overline{w}_2) + w_3(w_1w_2 + w_1\overline{w}_2 + w_1\overline{w}_2 + \overline{w}_1\overline{w}_2)$  $= \overline{w}_1w_2\overline{w}_3 + \overline{w}_1\overline{w}_2\overline{w}_3 + w_1\overline{w}_2\overline{w}_3 + w_1w_2w_3 + w_1\overline{w}_2w_3 + \overline{w}_1\overline{w}_2w_3$

6.8. Expansion in terms of  $w_1$  gives

$$f = \overline{w}_1 w_2 + \overline{w}_1 \overline{w}_3 + w_1 w_2$$

Further expansion in terms of  $w_2$  gives

$$f = \overline{w}_2(\overline{w}_1\overline{w}_3) + w_2(w_1 + \overline{w}_1 + \overline{w}_1\overline{w}_3)$$

=  $\overline{w}_1w_2 + \overline{w}_1w_2\overline{w}_3 + \overline{w}_1\overline{w}_2\overline{w}_3 + w_1w_2$

Further expansion in terms of  $w_3$  gives

$$f = \overline{w}_3(\overline{w}_1\overline{w}_2 + w_1w_2 + \overline{w}_1w_2 + \overline{w}_1w_2) + w_3(w_1w_2 + \overline{w}_1w_2)$$

$$= \overline{w}_1\overline{w}_2\overline{w}_3 + w_1w_2\overline{w}_3 + \overline{w}_1w_2\overline{w}_3 + \overline{w}_1w_2w_3 + w_1w_2w_3$$

#### 6.9. Proof of Shannon's expansion theorem

$$f(x_1, x_2, ..., x_n) = \overline{x}_1 \cdot f(0, x_2, ..., x_n) + x_1 \cdot f(1, x_2, ..., x_n)$$

This theorem can be proved using *perfect induction*, by showing that the expression is true for every possible value of  $x_1$ . Since  $x_1$  is a boolean variable, we need to look at only two cases:  $x_1 = 0$  and  $x_1 = 1$ .

Setting  $x_1 = 0$  in the above expression, we have:

$$\begin{array}{lll} f(0,x_2,...,x_n) &=& 1 \cdot f(0,x_2,...,x_n) + 0 \cdot f(1,x_2,...,x_n) \\ &=& f(0,x_2,...,x_n) \end{array}$$

Setting  $x_1 = 1$ , we have:

$$f(1, x_2, ..., x_n) = 0 \cdot f(0, x_2, ..., x_n) + 1 \cdot f(1, x_2, ..., x_n)$$

=  $f(1, x_2, ..., x_n)$

This proof can be performed for any arbitrary  $x_i$  in the same manner.

6.10. Derivation using  $\overline{f}$ :

$$\overline{f} = \overline{w}\overline{f}_{\overline{w}} + w\overline{f}_{w}$$

$$f = \left(\overline{w}\overline{f}_{\overline{w}} + w\overline{f}_{w}\right)$$

$$= \left(\overline{w}\overline{f}_{\overline{w}}\right) \cdot \left(\overline{w}\overline{f}_{w}\right)$$

$$= \left(w + f_{\overline{w}}\right)(\overline{w} + f_{w})$$

#### 6.11. Expansion in terms of $w_2$ gives

$$=\overline{w}_2(\overline{w}_1+\overline{w}_3)+w_2(w_1w_3)$$

f

Letting  $g = \overline{w}_1 + \overline{w}_3$ , we have

$$f = \overline{w}_2 g + w_2 \overline{g}$$

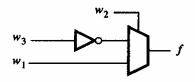

The corresponding circuit is

6.12. Expansion of f in terms of  $w_2$  gives

$$f = \overline{w}_2(\overline{w}_1 + \overline{w}_3) + w_2(w_1w_3)$$

$$= w_2 \oplus (\overline{w}_1 + \overline{w}_3)$$

$$= w_2 \oplus \overline{w_1w_3}$$

The cost of this multilevel circuit is 2 gates + 4 inputs = 6.

6.13. Using Shannon's expansion in terms of  $w_2$  we have

$$f = \overline{w}_2(\overline{w}_3 + \overline{w}_1w_4) + w_2(w_3\overline{w}_4 + w_1w_3)$$

$$= \overline{w}_2(\overline{w}_3 + \overline{w}_1w_4) + w_2(w_3(w_1 + \overline{w}_4))$$

If we let  $g = \overline{w}_3 + \overline{w}_1 w_4$ , then

$$f = \overline{w}_2 g + w_2 \overline{g}$$

Thus, two 3-LUTs are needed to implement f.

6.14. Any number of 5-variable functions can be implemented by using two 4-LUTs. For example, if we cascade the two 4-LUTs by connecting the output of one 4-LUT to an input of the other, then we can realize any function of the form

$$f = f_1(w_1, w_2, w_3, w_4) + w_5$$

$$f = f_1(w_1, w_2, w_3, w_4) \cdot w_5$$

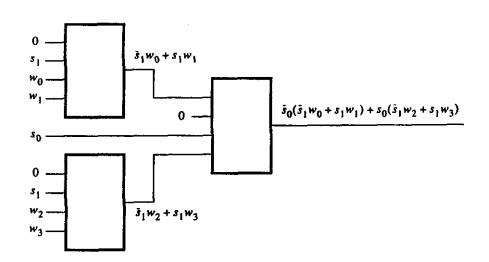

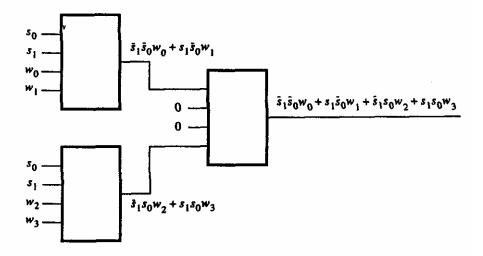

6.15. Expressing f in the form

$$f = \overline{s_1}\overline{s_0}w_0 + s_1\overline{s_0}w_1 + \overline{s_1}s_0w_2 + s_1s_0w_3$$

$$= \overline{s_0}(\overline{s_1}w_0 + s_1w_1) + s_0(\overline{s_1}w_2 + s_1w_3)$$

leads to the circuit.

### Alternatively, directly using the expression

$$f = \overline{s}_1 \overline{s}_0 w_0 + s_1 \overline{s}_0 w_1 + \overline{s}_1 s_0 w_2 + s_1 s_0 w_3$$

leads to the circuit.

6.16. Using Shannon's expansion in terms of  $w_3$  we have

$$f = \overline{w}_3(w_2) + w_3(w_1 + \overline{w}_2)$$

=  $\overline{w}_3(w_2) + w_3(\overline{w}_2 + w_2w_1)$

The corresponding circuit is

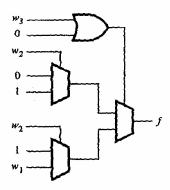

6.17. Using Shannon's expansion in terms of  $w_3$  we have

$$f = w_3(\overline{w}_1 + w_1\overline{w}_2) + \overline{w}_3(w_1 + \overline{w}_1w_2)$$

The corresponding circuit is

- 6.18. The code in Figure P6.2 is a 2-to-4 decoder with an enable input. This style of code is a poor choice because its meaning is not readily apparent. Better choices of code that represents a 2-to-4 decoder are shown in Figures 6.30 and 6.46.

- 6.19. LIBRARY ieee ; USE ieee.std\_logic\_1164.all ;

```

ENTITY prob6_19 IS

PORT ( w : IN STD_LOGIC_VECTOR(1 TO 3);

f : OUT STD_LOGIC );

END prob6_19;

ARCHITECTURE Behavior OF prob6_19 IS

BEGIN

WITH w SELECT

f <= '0' WHEN "001",

'0' WHEN "110",

'1' WHEN OTHERS ;

END Behavior ;

```

6.20. LIBRARY ieee ; USE ieee.std\_logic\_1164.all ;

> ENTITY prob6\_20 IS PORT ( w : IN STD\_LOGIC\_VECTOR(1 TO 3); f : OUT STD\_LOGIC ); END prob6\_20;

ARCHITECTURE Behavior OF prob6\_20 IS BEGIN WITH w SELECT f <= '0' WHEN "000", '0' WHEN "100", '0' WHEN "111", '1' WHEN OTHERS ;

END Behavior;

6.21. LIBRARY ieee ; USE ieee.std\_logic\_1164.all ;

> ENTITY prob6\_21 IS PORT ( w : IN STD\_LOGIC\_VECTOR(3 DOWNTO 0) ; y : OUT STD\_LOGIC\_VECTOR(1 DOWNTO 0) ) ; END prob6\_21 ;

ARCHITECTURE Behavior OF prob6\_21 IS BEGIN WITH w SELECT y <= "00" WHEN "0001", "01" WHEN "0010", "10" WHEN "0100", "11" WHEN OTHERS ;

END Behavior;

6.22. LIBRARY ieee ; USE ieee.std\_logic\_1164.all ;

> ENTITY prob6\_22 IS PORT ( w : IN STD\_LOGIC\_VECTOR(7 DOWNTO 0) ; y : OUT STD\_LOGIC\_VECTOR(2 DOWNTO 0) ); END prob6\_22 ;

...con't

ARCHITECTURE Behavior OF prob6\_22 IS BEGIN y <= "000" WHEN w = "00000001" ELSE "001" WHEN w = "00000010" ELSE "010" WHEN w = "00000100" ELSE "011" WHEN w = "00001000" ELSE "100" WHEN w = "00100000" ELSE "101" WHEN w = "00100000" ELSE "110" WHEN w = "01000000" ELSE "111" ; END Behavior ;

6.23. First define a set of intermediate variables

$i_0 = \overline{w}_7 \overline{w}_6 \overline{w}_5 \overline{w}_4 \overline{w}_3 \overline{w}_2 \overline{w}_1 w_0$   $i_1 = \overline{w}_7 \overline{w}_6 \overline{w}_5 \overline{w}_4 \overline{w}_3 \overline{w}_2 w_1$   $i_2 = \overline{w}_7 \overline{w}_6 \overline{w}_5 \overline{w}_4 \overline{w}_3 w_2$   $i_3 = \overline{w}_7 \overline{w}_6 \overline{w}_5 \overline{w}_4 w_3$   $i_4 = \overline{w}_7 \overline{w}_6 \overline{w}_5 w_4$   $i_5 = \overline{w}_7 \overline{w}_6 w_5$   $i_6 = \overline{w}_7 w_6$   $i_7 = w_7$

Now a traditional binary encoder can be used for the priority encoder

| <b>y</b> o | = | $i_1 + i_3 + i_5 + i_7$ |

|------------|---|-------------------------|

| $y_1$      | = | $i_2 + i_3 + i_6 + i_7$ |

| $y_2$      | = | $i_4 + i_5 + i_6 + i_7$ |

6.24. LIBRARY ieee ; USE ieee.std\_logic\_1164.all ;

> ENTITY prob6\_24 IS STD\_LOGIC\_VECTOR(7 DOWNTO 0); PORT (w : IN y : OUT STD\_LOGIC\_VECTOR(2 DOWNTO 0); z : OUT STD\_LOGIC); END prob6\_24; **ARCHITECTURE Behavior OF prob6..24 IS** BEGIN y <= "111" WHEN w(7) = '1' ELSE "110" WHEN w(6) = '1' ELSE "101" WHEN w(5) = '1' ELSE "100" WHEN w(4) = '1' ELSE "011" WHEN w(3) = '1' ELSE "010" WHEN w(2) = '1' ELSE "001" WHEN w(1) = '1' ELSE "000": z <= '0' WHEN w="00000000" ELSE '1'; END Behavior;

6.25. LIBRARY ieee ; USE ieee.std\_logic\_1164.all; ENTITY prob6\_25 IS STD\_LOGIC\_VECTOR(7 DOWNTO 0); PORT (w : IN y : OUT STD\_LOGIC\_VECTOR(2 DOWNTO 0); z : OUT STD\_LOGIC); END prob6\_25; **ARCHITECTURE Behavior OF prob6\_25 IS** BEGIN PROCESS (w) BEGIN IF w(7) = '1' THEN y <= "111"; ELSIF w(6) = '1' THEN y <= "110"; ELSIF w(5) = '1' THEN y <= "101"; ELSIF w(4) = '1' THEN y <= "100"; ELSIF w(3) = '1' THEN y <= "011"; ELSIF w(2) = '1' THEN y <= "010"; ELSIF w(1) = '1' THEN y <= "001"; ELSE y <= "000"; END IF; IF w = "00000000" THEN z <= '0' ; ELSE z <= '1' ; END IF; END PROCESS ; END Behavior;

LIBRARY ieee ; USE ieee.std\_logic\_1164.all ; ENTITY if2to4 IS PORT ( w : IN STD\_LOGIC\_VECTOR(1 DOWNTO 0) ; En : IN STD\_LOGIC ; y : OUT STD\_LOGIC\_VECTOR(3 DOWNTO 0) ) ; END if2to4 ;

... con't

6.26.

```

ARCHITECTURE Behavior OF if2to4 IS

BEGIN

PROCESS (En, w)

BEGIN

IF En = '0' THEN

y <= "0000";

ELSE

IF w = "00" THEN

y <= "0001";

ELSIF w = "01" THEN

y <= "0010";

ELSIF w = "10" THEN

y <= "0100";

ELSE

y <= "1000";

END IF:

END IF;

END PROCESS ;

END Behavior;

LIBRARY ieee ;

USE ieee.std_logic_1164.all;

PACKAGE if2to4_package IS

COMPONENT if2to4

PORT (w : IN

STD_LOGIC_VECTOR(1 DOWNTO 0);

En : IN

STD_LOGIC;

y : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END COMPONENT;

END if2to4_package;

LIBRARY ieee;

USE ieee.std_logic_1164.all:

USE work.if2to4_package.all;

ENTITY h3to8 IS

PORT (w : IN

STD_LOGIC_VECTOR(2 DOWNTO 0);

En : IN

STD_LOGIC ;